# **Chapter 9**

# Memory Devices, Circuits, and Subsystem Design

The 8088 and 8086 Microprocessors, Triebel and Singh

## Introduction

- 9.1 Program and Data Storage Memory—•

- 9.2 Read-Only Memory—•

- 9.3 Random Access Read/Write Memories—•

- 9.4 Parity, Parity Bit, and Parity-Checker/Generator Circuit

- 9.5 FLASH Memory

- 9.6 Wait-State Circuitry-

- 9.7 8088/8086 Microcomputer System Memory Interface Circuitry—•

# 9.1 Program and Data Storage Memory- The Memory Unit

- Memory—provides the ability to store and retrieve digital information Instructions of a program

- Data to be processed

- Results produced by processing

- Organization of the Microcomputer memory unit

- Secondary storage—stores information that is not currently in use

- Slow-speed

Memory unit

Data

storage

memory

MPU

Secondary

storage

memory

Primary storage memory

Program

storage

memory

- Very large storage capacity

- Implemented with magnetic/optical storage devices—in PC

- Hard disk drive

- Floppy disk drive

- Zip drive

- Primary storage—stores programs and data that are currently active

- High-speed

- Smaller storage capacity

- Implemented with semiconductor memory

- Partitioning of Primary Storage

- Program storage memory—holds instructions of the program and constant information such as look-up tables

- EPROM (BIOS in PC)

- FLASH memory

- DRAM (volatile code storage in a PC)

- Data storage memory—holds data that frequently changes

The 8088 and 8086 Misuoprastle information to barppeessed by a program 3

- SRAM

- DRAM (PC)

#### 9.2 Read-Only Memory- Types

Read-only memory (ROM)

- Used for storage of machine code of program

- Stored information can only be read by the MPU

- Information is nonvolatile—not lost when power turned off

• Types:

- **ROM**—mask-programmable read only memory

- Programmed as part of manufacturing process

- Lowest cost

- High volume applications

- PROM—one-time programmable read-only memory

- Permanently programmed with a programming instrument

- EPROM—erasable programmable read-only memory

- Programmed like a PROM

- Erasable by Ultraviolet light

- Electrically alterable ROM-like devices

- FLASH memory

- EEROM (E2ROM)

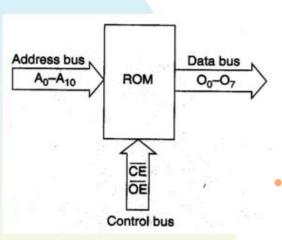

#### 9.2 Read-Only Memory- Block Diagram

- Block diagram of the ROM, PROM, and EPROM are essentially the same

- **Signal interfaces**

- Address bus (A10-A0 )—MPU inputs address information that selects the storage location to be accessed

- Data Bus (D7-D0)—information from the accessed storage location output to be read by MPU

- Control bus—enables device and/or enables output from device

- CE\* = chip enable—active 0; 1 low-power stand by mode

- OE\* = output enable—active 0; 1 high-Z state

- Byte capacity- number of bytes a device can store

- Calculated from number of address bits

- EX: Address = 11-bit address

Storage capacity = 211 = 2048 bytes

- Organization—how the size of a ROM is described

- Formed from capacity and data bus width

- EX: 2048 X 8 or just 2K X 8

- Storage density—number of bits of storage in a ROM

- Calculated from byte capacity and data width

The 8088 a EX: Storage density = 2048 X 8 = 16384 bits (16K bits)

# 9.2 Read-Only Memory- Organization and Capacity

Example:

A ROM device has 15 address lines and 8 data lines. What are the address range, byte capacity, organization, and storage density?

Solution:

Address range

A14-A0 = 000 0000 0000 2 · 111 1111 1111 11112

= 0000H · 7FFFH

Byte capacity

215 = 32,768 bytes = 32K bytes

Organization

32,768 X 8 bit

Storage density

32,768 x 8 = 262144 bits = 256K bits

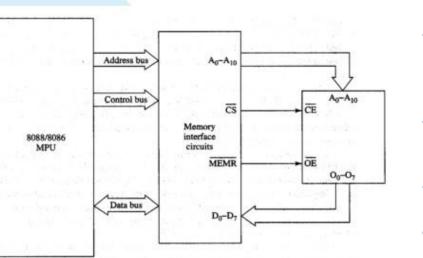

#### 9.2 Read-Only Memory- Operation

- **Read operation**

- MPU outputs address and control information on its bus.

- Interface circuit applies Address A10-A0 to the address inputs of the ROM to select a specific byte wide storage location

- Interface circuits decode additional address bits to produce a chip select output

- Logic 0 at CS\* applied to the CE\* input of the ROM to enable it for operation

- Memory interface circuitry produces appropriately timed MEMR\* output

- MEMR\* applied to OE\* input of the ROM to enable the information at the addressed storage location onto the output bus D7-D0

- Memory interface supplies the byte of data from the ROM to the MPUs data bus

- MPU reads the byte of data from the ROM from its data bus sinch

The 8088 and 8086 Microprocessors, Triebel and Singh

| 9.2 Read-Only Memory- Standard EPROM ICs | 9.2 Read-Only | / Memory- | Standard | <b>EPROM ICs</b> |

|------------------------------------------|---------------|-----------|----------|------------------|

|------------------------------------------|---------------|-----------|----------|------------------|

EPROM part numbers formed by adding the prefix "27" to the device total Kbits of storage capacity

• Examples:

- 16K bit EPROM · 2716

- 32K bit EPROM · 2732

- 1M bit EPROM · 27C010

- Most EPROM available in byte wide organization

• Examples:

- 2764 · 8K X 8

- 27C020 · 256K X8

- NMOS versus CMOS process

- Manufacturing processes used to make EPROMs

- NMOS=N-channel metal-oxide semiconductor

- CMOS= complementary symmetry metaloxide semiconductor

- "CMOS" designated by "C" in part number

NMOS—older devices such as 2716 and 2732

The 8088 and 8°86 CMOS all newer devices 27C64 and up

| EPROM  | Density<br>(bits) | Capacity<br>(bytes) |

|--------|-------------------|---------------------|

| 2716   | 16K               | 2K×8                |

| 2732   | 32K               | 4K×8                |

| 27C64  | 64K               | 8K×8                |

| 27C128 | 128K              | 16K×8               |

| 27C256 | 256K              | 32K × 8             |

| 27C512 | 512K              | 64K×8               |

| 27C010 | 1M                | 128K × 8            |

| 27C020 | 2M                | 256K × 8            |

| 27C040 | 4M                | 512K×8              |

#### 9.2 Read-Only Memory- Pin Layouts

| 270512         | 27C128         | 27C64 | 2732A | 2716           | Pin  |

|----------------|----------------|-------|-------|----------------|------|

| A.18           | V,             | Vm    |       |                | 1    |

| A.2            | A.2            | A.2   |       |                | 2    |

| A.,            | A,             | A,    | A,    | Α,             | 3    |

| A.             | A.             | A.    | A     | A <sub>s</sub> | 4    |

| As             | As             | As    | As    | As .           | 5    |

| A.             | A.             | A.    | A.    | A.             | 6    |

| A <sub>3</sub> | A.,            | A2    | A.    | A.             | 7    |

| Ag             | A <sub>3</sub> | A.2   | A2    | A2             | 8    |

| Α,             | A,             | A,    | A,    | A,             | 9    |

| Ag             | Ao             | A     | Ao    | Ao             | 10   |

| 0.             | 00             | 0.    | 0.    | 00             | 11   |

| 0,             | 0,             | 0,    | 0,    | 0,             | 12   |

| 02             | 0,             | 0,    | 0,    | 0,             | 13   |

| Ged            | Gent           | Ged   | Ged   | Get            | 1 14 |

| 1.5            |         |    | 5e    |

|----------------|---------|----|-------|

| V.             | 1       | 28 | DV cc |

| Ais            | 2       | 27 | A     |

| A,C            | 3       | 26 | A     |

| A.C            | 4       | 25 | DA.   |

| A,C            | 5       | 24 | DA.   |

| A.C            | 5       | 23 | DAn   |

| A, [           | 7 27025 | 22 | DOE   |

| A2             | 8 2/025 | 21 | DA10  |

| A, 🗆           | 9       | 20 | DCE   |

| A <sub>0</sub> | 10      | 19 | 0,    |

| 0,0            | 11      | 18 | Þo.   |

| 0, 0           | 12      | 17 | 00    |

| 0,□            | 13      | 16 | Do.   |

| Out D          | 14      |    | 10    |

| Pin | 2716           | 2732A  | 27C64 | 27C128 | 27C512          |

|-----|----------------|--------|-------|--------|-----------------|

| 28  | 1              |        | Voc   | Vcc    | Vcc             |

| 27  |                |        | PGM   | PGM    | An              |

| 26  | Vcc            | Vcc    | N.C.  | A.,    | A <sub>t2</sub> |

| 25  | A <sub>8</sub> | A      | A     | As     | As              |

| 24  | A              | A      | A     | A.     | Ag              |

| 23  | Va             | An     | A.,   | A.,    | Ast             |

| 22  | ŌĒ             | OE/Vpp | ŌĒ    | ŌE     | OE/V            |

| 21  | A.0            | Aus    | A10   | A.,    | A.10            |

| 20  | <b>CE</b>      | ĈĒ     | ĈĒ    | CE     | CE              |

| 19  | 0,             | 0,     | 0,    | 0,     | 0,              |

| 18  | 0.             | 0.     | 0,    | 0.     | 0.              |

| 17  | 0.             | 0.     | 0,    | 0.     | 0,              |

| 16  | 0.             | 0.     | 0.    | 0.     | 0.              |

| 15  | 0.             | 0.     | 0.    | 0,     | 0.              |

**EPROM** pin layouts are designed for compatibility

- Permit easy upgrade from lower to higher density

- Publish pin layouts of future densities

- Allows design of circuit boards to support drop in upgrade to higher densities

- Most pins are independent and serve a common function for all densities

- Examples:

- pin 10- A0

- pin 11--00

- pin 14- Gnd

Some have one multi-function

pin• OE\*/Vpp

• Vpp mode during programming only

The 8088 and 8086 Microprocessors, Triebel and Singh

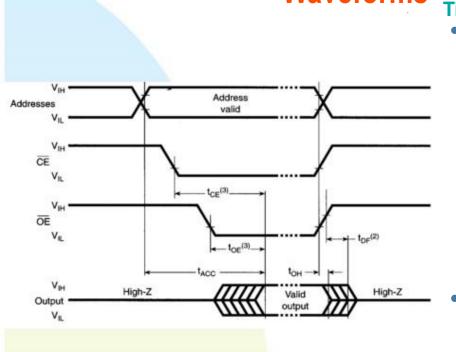

# 9.2 Read-Only Memory- EPROM Switching Waveforms

- Timing of the read operation

- Output data is not immediately available at the outputs

- Delays exist between the application of the address,CE\* and OE\* signals and the occurrence of a valid output

- tacc= access time—address to valid output delay time

- tCE= chip-enable time—chip enable to valid output delay

- tOE=output-enable time—output enable to valid data delay

- To assure that the MPU reads valid data, these inputs must be applied at the appropriate times

- Responsibility of the memory interface circuitry

- Another delay occurs at the removal of OE\* before the outputs lines are returned to the high-Z state

The 8088 and 8086 Microprocessors, Trichip deselect time—time for 10 the outputs to recover

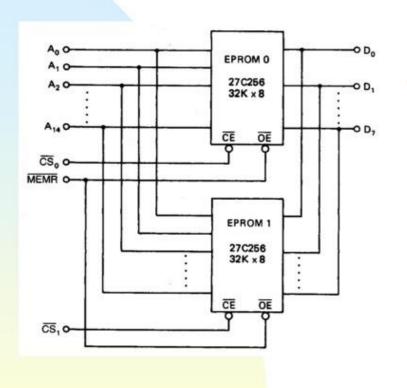

# 9.2 Read-Only Memory- Expanding Byte Capacity

Many applications require more ROM capacity than is available in a single device

- Need more bytes of storage

- Connects to a wider data bus

Expanding byte capacity with 2 EPROMS

- Connect address bus lines in parallel

- Connect output lines in parallel

- Connect OE\* in parallel

- Enable chips with separate chip selects

- Address bit A15 decoded to produce CS0\* and CS1\*

- A15=0 · CS0\*

- A15=1 · CS1\*

- Implemented with inverting buffer

- Byte capacity

2<sub>16</sub> = 64K bytes

• Organization

64K X 8 bit

Storage density

The 8088 and 8086 Micropro 2 X 32 Ki x 8 ≅ 5 72Khbits

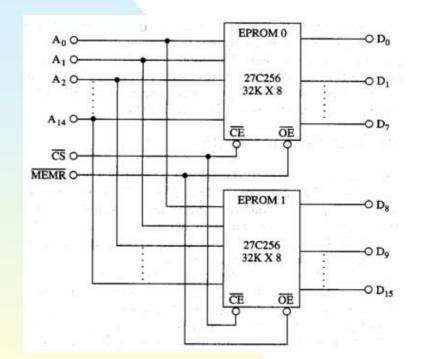

#### 9.2 Read-Only Memory- Expanding Word Length

- Expanding word length with 2 EPROM

- Connecting to 8086 16-bit data bus

- Connect address bus lines in parallel

- Connect CE\* in parallel

- Connect OE\* in parallel

- 8 data outputs of EPROM 0 used to supply the lower data bus lines D0-D7

- 8 data outputs of EPROM 1 used to supply the upper 8 data bus lines D8-D15

- Byte capacity

- 2 X 215 = 64K byte

- Organization 32K X 16 bit

- Storage density 32K x 16 = 512K bits

#### 9.3 Random Access Read/Write Memories-

#### **Types of RAMs**

Random Access Read/Write Memory (RAM)

- Used for temporary storage of data and program information

- Stored information can be altered by MPU—read or written

- Information read from RAM

- Modified by processing

- Written back to RAM for reuse at a later time

- Information normally more frequently randomly accessed than ROM

- Information is volatile— lost when power turns off

- Types:

- Static RAM (SRAM)— data once entered remains valid as long as power supply is not turned off

- Lower densities

- Higher cost

- Higher speeds

• Dynamic RAM (DRAM)—data once entered requires both the power to be maintained and a periodic refresh

- Higher densities

- Lower cost

- Lower speeds

- Refresh requires additional circuitry

The 8088 and 8086 Microprocessors, Triebel and Singh

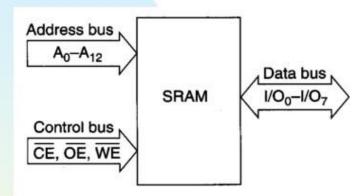

#### 9.3 Random Access Read/Write Memories-SRAM Block Diagram

#### Signal interfaces

- Address bus (A12-A0)—MPU inputs address information that selects the storage location to be accessed

- Data Bus (I/O7-I/O0)—input/output of information for the accessed storage location from/to MPU

- Control bus—enables device, enables output from device, and selects read/write operation

- CE\* = chip enable—active 0

- OE\* = output enable—active 0

- WE\* = write enable

- 0 = write to RAM

- 1 = read from RAM

#### 9.3 Random Access Read/Write Memories-Standard SRAM ICs

| SRAM    | Density<br>(bits) | Organization |

|---------|-------------------|--------------|

| 4361    | 64K               | 64K × 1      |

| 4363    | 64K               | 16K×4        |

| 4364    | 64K               | 8K × 8       |

| 43254   | 256K              | 64K×4        |

| 43256A  | 256K              | 32K × 8      |

| 431000A | 1M                | 128K × 8     |

- Part numbers vary widely by manufacturer—Hitachi/NEC use "43xxx SRAMs are available in a variety of densities and organization

- Typical SRAM densities

- 64K bit

- 256K bit

- 1M bit

- Typical organizations of the 64K bit

SRAM • 64K X 1 bit • 16K X 4 bit • 8K X 8 bit

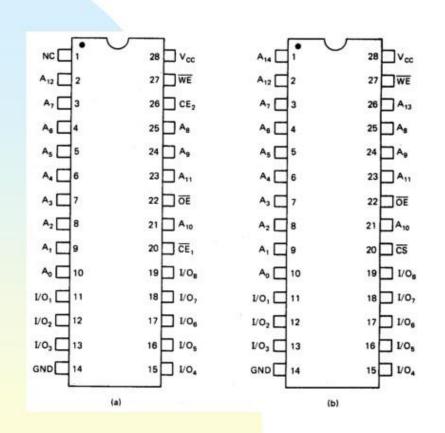

#### 9.3 Random Access Read/Write Memories- Pin Layout of SRAMs

4364 and 43256A pin layouts are designed for compatibility 4364 pin configuration (Fig a)

- A12-A0 · 13-bit address 2<sub>13</sub> = 8K bytes

- I/O7-I/O0 · byte wide

- Pin 1 NC = no connect

- Pin 27 WE\*

- Pin 20 CE1\* · active 0

- Pin 26 CE2 · active 1

- Pin 22 · OE\*

- Pin 28 Vcc

- Pin 14 GND

- 43256A differences (Fig b)

- Pin 1 · A14

- Pin 26 · A13

- Pin 20 called CS\* (function unchanged)

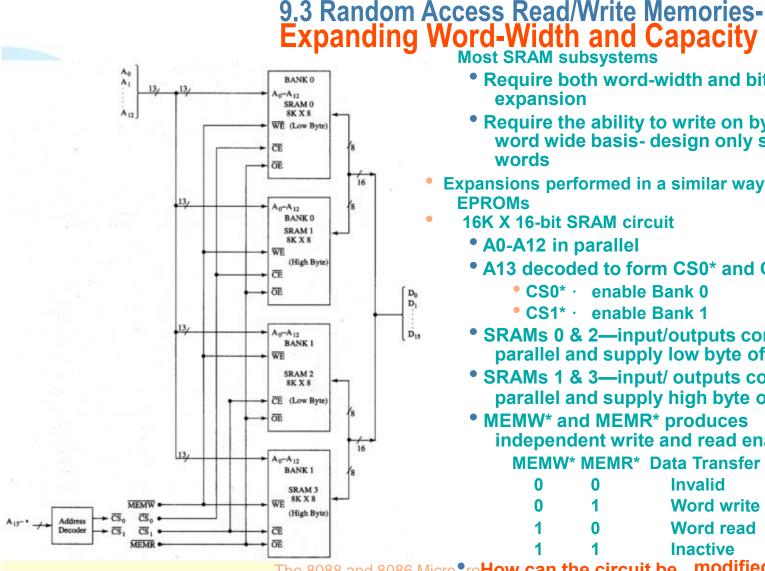

- Require both word-width and bit capacity expansion

- Require the ability to write on byte-wide or word wide basis- design only supports words

- Expansions performed in a similar way as for **EPROMs**

- 16K X 16-bit SRAM circuit

- A0-A12 in parallel

- A13 decoded to form CS0\* and CS1\*

- CS0\* · enable Bank 0

- CS1\* · enable Bank 1

- SRAMs 0 & 2—input/outputs connected in parallel and supply low byte of data bus

- SRAMs 1 & 3—input/ outputs connected in parallel and supply high byte of data bus

- MEMW\* and MEMR\* produces independent write and read enables

- **MEMW\* MEMR\*** Data Transfer

| 0 | 0 | Invalid    |

|---|---|------------|

| 0 | 1 | Word write |

| 1 | 0 | Word read  |

| 1 | 1 | Inactive   |

The 8088 and 8086 Micro<sup>•</sup>roHow can the circuit be modified to support

byte wide write?

#### 9.3 Random Access Read/Write Memories-Standard Read/Write Cycle Times

| Part number | Read/write cycle time |

|-------------|-----------------------|

| 4364-10     | 100 ns                |

| 4364-12     | 120 ns                |

| 4364-15     | 150 ns                |

| 4364-20     | 200 ns                |

- Speed of a SRAM identified as read/write cycle time

- Variety of speeds available—4364 available in speeds ranging from 100ns to 200ns

- Shorter the cycle time the better.

- Designated by a dash speed indicator following the part number

- -10 = 100ns

- -12 = 120ns

#### 9.3 Random Access Read/Write Memories-DRAM Block Diagram

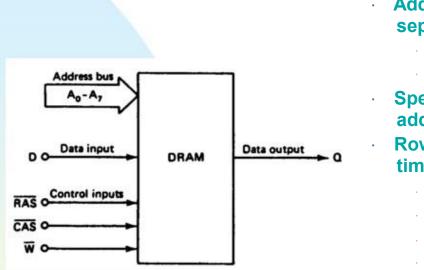

#### DRAM signal interfaces

- Address multiplexed in external circuitry into a separate row and column address

- Row address = A<sub>7</sub>-A<sub>0</sub>

- Column address = A15-A8

- Special RAS\* and CAS\* inputs used to strobe address into DRAM

Row and column addresses applied at different times to address inputs A<sub>0</sub> through A<sub>7</sub>

- Row address first

- Column address second

- Known as "RAS before CAS"

- Address reassembled into 16-bit address inside DRAM

- Frequently data organizations are X1, X2, and X4

- Separate data inputs and outputs

- Data input labeled D

- Data output labeled Q

- Read/write (W) input signals read or write operation

| 9.3 Random Access | <b>Read/Write</b> | <b>Memories-</b> |

|-------------------|-------------------|------------------|

| Standard DRAM     | Cs                |                  |

| DRAM   | Density<br>(bits)                        | Organization |

|--------|------------------------------------------|--------------|

| 2164B  | 64K                                      | 64K×1        |

| 21256  | 256K                                     | 256K×1       |

| 21464  | 256K                                     | 64K×4        |

| 421000 | 1M                                       | 1M×1         |

| 424256 | 1M                                       | 256K×4       |

| 44100  | 4M                                       | 4M×1         |

| 44400  | 4M                                       | 1M×4         |

| 44160  | 4M                                       | 256K×16      |

| 416800 | 16M                                      | 8M×2         |

| 416400 | 16M                                      | 4M×4         |

| 416160 | 16M                                      | 1M×16        |

|        | and a second second second second second |              |

- DRAMs are available in a variety of densities and organization

- Typical DRAM densities

- 64K bit

- 256K bit

- 1M bit, Etc.

- Modern DRAMS as large as 1G bit

- Typical organizations of the 4M bit DRAM

- 4M X 1 bit

- 1M X 4 bit

- Modern higher density devices also available in X8, X16, and X32 organizations

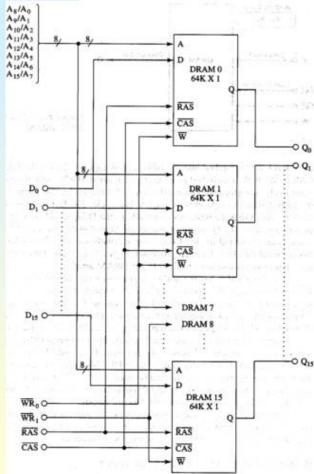

#### 9.3 Random Access Read/Write Memories-Circuit Design using DRAMS

Sixteen 64KX1-bit DRAMs interconnected to form a 64K word memory subsystem—1M-bits of memory

- **Circuit connections**

- 8 multiplexed address inputs of all devices connected in parallel

- RAS and CAS lines of all devices connected in parallel

- Data input and output lines

- Independent data lines arranged to form a 16-bit wide output bus

- Independent input lines arranged to form a 16-bit wide input bus

- In most microprocessor applications input and output lines are connected together

- Read/write lines

- W inputs of upper 8 DRAMs connected together and driven by WR0\*

- W inputs of lower 8 DRAMs connected together and driven by WR1\*

- Permits byte-wide or word-wide reads and writes

The 8088 and 8086 Microprocessors, Triebel and Singh

# *9.3 Random Access Read/Write Memories*

- The primary memory section of a microcomputer system is normally formed from both read-only memories and random access read/write memories (RAM)

- RAM is different from ROM in two ways:

- Data stored in RAM is not permanent in nature.

- RAM is volatile that is, if power is removed from

RAM, the stored data are lost.

- RAM is normally used to store temporarily data and application programs for execution.

# *9.3 Random Access Read/Write Memories*

- □ Static and dynamic RAMs

- For a static RAM (SRAM), data remain valid as long as the power supply is not turned off.

- For a dynamic RAM (DRAM), we must both keep the power supply turned on and periodically restore the data in each location.

- The recharging process is known as *refreshing* the DRAM.

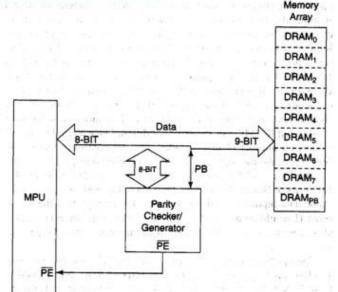

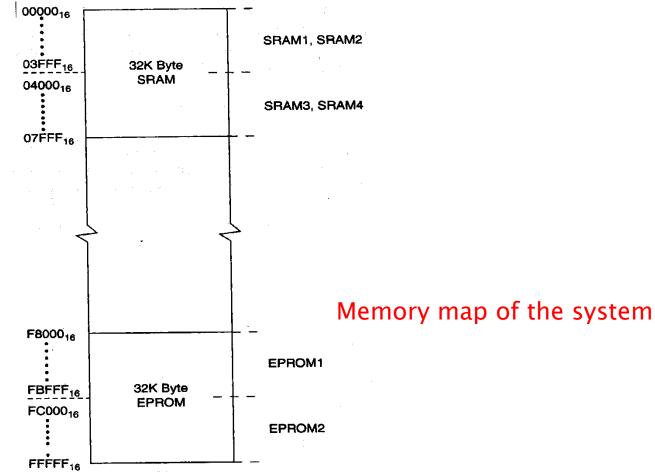

#### 9.4 Parity, The Parity Bit, and Parity-Checker/Generator Circuit- Parity and the Parity Bit

Data exchange between the MPU and data memory subsystem in a microcomputer must be done without error

- Sources of errors

- Emissions that affect data on the data bus line

- Electrical noise signals—spikes or transients that affect data on data lines

- Defective bit in a DRAM

- Soft errors of DRAM

- Solutions for improving data integrity

- 1. Parity

- 2. Error correction code (ECC)

- Parity most frequently used

- Parity bit

- Add an additional bit of data to each byte or word of data so that all elements of data have the same parity

Extra bit is known as the "parity bit"

- Even parity—element of data has an even number of bits at the 1 logic level

- Odd parity—element of data has an odd number of bit that are logic 1

- Circuitry added to the DRAM memory interface to generate an appropriate parity bit on writes to memory

- Extra DRAM required to store the parity bit

- Circuitry checks element of data from correct parity during read operations

- Parity errors (PE) reported to MPU usually as an

The 8088 and 80 interrupt rocessors, Triebel and Singh

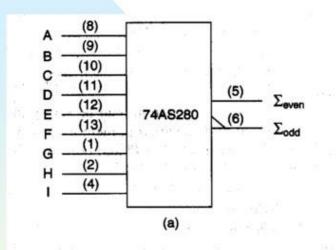

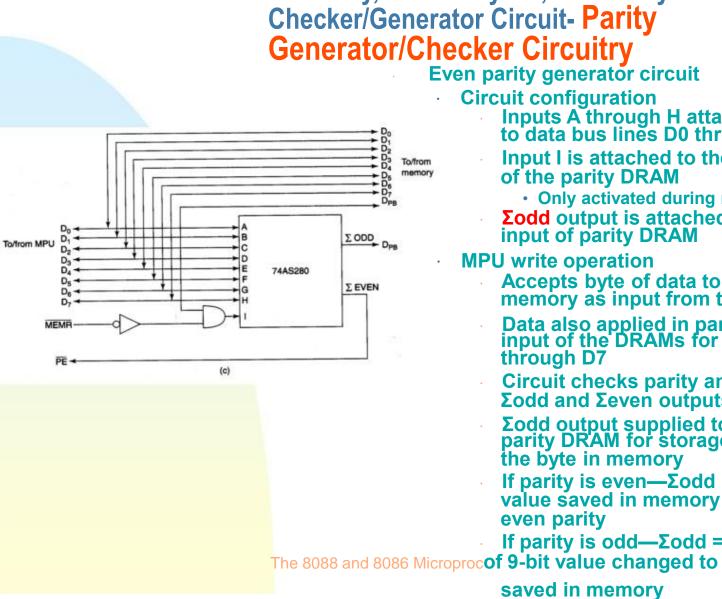

#### 9.4 Parity, The Parity Bit, and Parity-Checker/Generator Circuit- Parity Generator/Checker Circuitry

| NUMBER OF INPUTS A   | OUTPUTS       |      |

|----------------------|---------------|------|

| THRU I THAT ARE HIGH | $\Sigma EVEN$ | ΣODD |

| 0,2,4,6,8            | н             | L.   |

| 1,3,5,7,9            | L             | н    |

Parity generator/checker circuit—circuit added to the data memory interface to implement parity

- May be implemented with a 74AS280 parity generator/checker IC

- 9 inputs A through I

- Two outputs Σodd and Σeven

- **Operation:**

- Even number of inputs are logic 1  $\cdot$

- $\Sigma$ even = 1 and  $\Sigma$ odd = 0

- Signals that input has even parity

- Odd number of inputs are logic 1<sup>.</sup>

- $\Sigma even = 0$  and  $\Sigma odd = 1$

- Signals that input has odd parity

# 9.4 Parity, The Parity Bit, and Parity-

- Inputs A through H attach in parallel to data bus lines D0 through D7

- Input I is attached to the data output

- Only activated during read operations **Σodd** output is attached to the data

- Accepts byte of data to be written to memory as input from the data bus

- Data also applied in parallel to the input of the DRAMs for data lines D0

- **Circuit checks parity and generates Σodd and Σeven outputs**

- **Σodd output supplied to input of parity DRAM for storage along with the byte in memory**

- If parity is even— $\Sigma$ odd = 0 and 9-bit value saved in memory still has

- If parity is odd— $\Sigma$ odd = 1 and parity

The 8088 and 8086 Microprocof 9-bit value changed to even and 37

#### 9.4 Parity, The Parity Bit, and Parity-Checker/Generator Circuit- Parity Generator/Checker Circuitry

Read operation:

- Accepts 9-bit wide input from data outputs of the DRAM subsystem

- Checks the number of bits that are at the 1 logic level

- Produces appropriate logic level signals at odd parity and even parity outputs

If parity is even—Σeven = 1 and parity is correct

- Memory operation completes normally

- If parity is odd—Σeven = 0 and a parity error is detected

- Error condition signaled to MPU by logic 0 at PE\*

- Usually applied as NMI input to the MPU

- Must get serviced before executing next instruction

- MPU may

- Reattempt memory access

- Initiate an orderly shut

The 8088 and 8086 Microprocessors, Triebe down of application 3

38

- Data storage memory

- □ Information that frequently changes is normally implemented with random access read/write memory (RAM).

- □ If the amount of memory required in the microcomputer is small, the memory subsystem is usually designed with SRAMs.

- DRAMs require refresh support circuit which is not warranted if storage requirement are small.

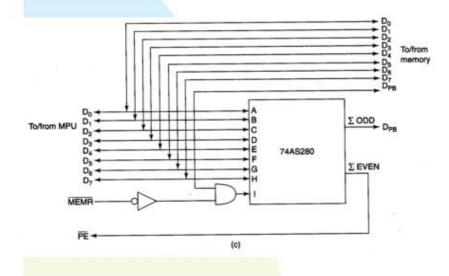

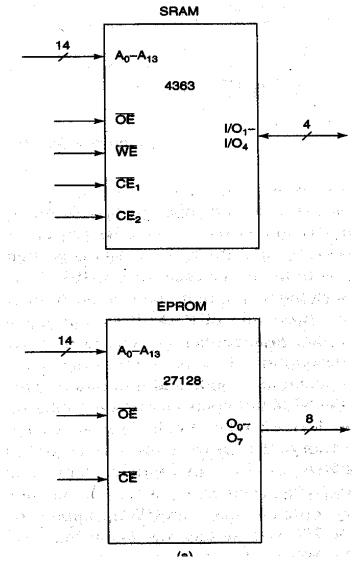

EXAMPLE

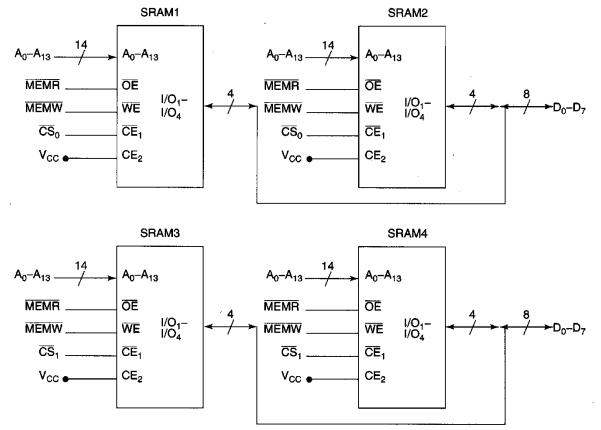

Design a memory system consisting of 32Kbytes of R/W memory and 32Kbytes of ROM memory. Use SRAM devices to implement R/W memory and EPROM devices to implement ROM memory. The memory devices to be used are shown below. R/W memory is to reside over the address range 00000H through 07FFFH and the address range of ROM memory is to be F8000H through FFFFFH. Assume that the 8088 microprocessor system bus signals that follow are available for use: Ao through A19, D0 through D7, MEMR', MEMW'.

SOLUTION:

First let us determine the number of SRAM devices needed.

No. of SRAM devices =  $32Kbyte/(16K \times 4) = 4$ To provide an 8-bit data bus, two SRAMs must be connected in parallel. Two pairs connected in this way are then placed in series to implement the R/W address range, and each pair

implements 16Kbytes.

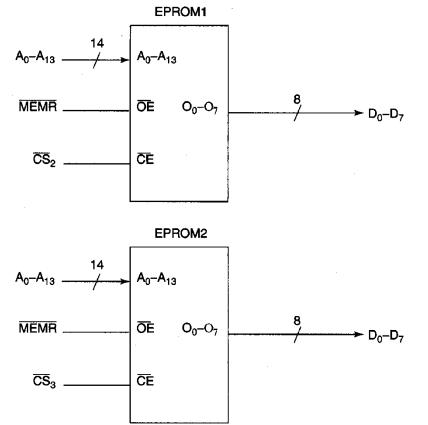

Next let us determine the number of EPROM devices needed.

No. of EPROM devices = 32Kbyte/16Kbyte = 2 These two devices must be connected in series to implement the ROM address range and each implement 16Kbytes of storage.

#### SOLUTION:

RAM memory organization for the system design

SOLUTION:

ROM memory organization for the system design

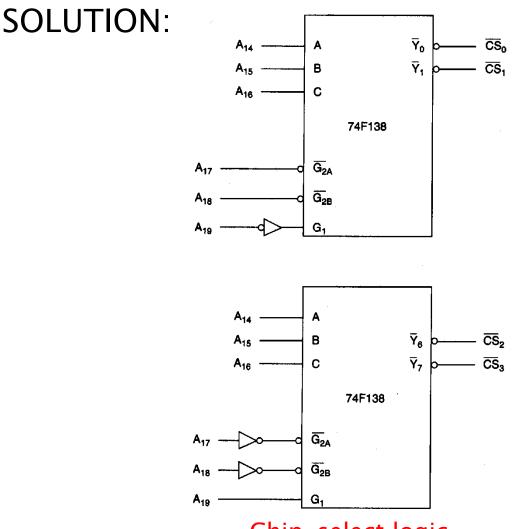

A<sub>19</sub>.....A<sub>0</sub> SOLUTION:  $00000_{16} = 0000 \ 0000 \ 0000 \ 0000$  $03FFF_{16} = 0000 0011 1111 1111 1111$  $\overline{CS}_0$  $04000_{16} = 0000 \ 0100 \ 0000 \ 0000$  $07FFF_{16} = 0000 \ 0111 \ 1111 \ 1111 \ 1111$  $\overline{CS}_1$  $F8000_{16} = 1111 \ 1000 \ 0000 \ 0000 \ 0000$  $\mathbf{FBFFF}_{16} = \underbrace{1111}_{011} \underbrace{1011}_{1111} \underbrace{1111}_{1111}$  $\overline{CS}_{2}$  $FC000_{16} = 1111 \ 1100 \ 0000 \ 0000 \ 0000$  $\text{FFFFF}_{16} = \underbrace{1111}_{111} \underbrace{11}_{1111} \underbrace{1111}_{1111} \underbrace{1111}_{1111}$  $\overline{CS}_{2}$

Address range analysis for the design of chip select signals

Chip-select logic