# تقدم لجنة ElCoM الاكاديمية

دفتر لمادة:

الكترونيات رقمية

من شرح:

د.رولب طوالبه

### DIGITAL ELECTRONICS

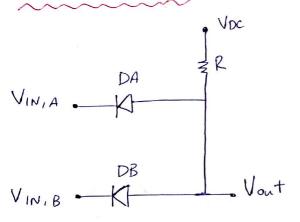

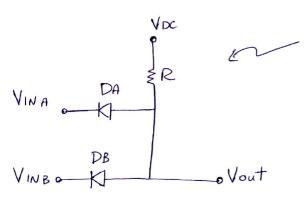

### 2.5 Diode - Resistore Logic

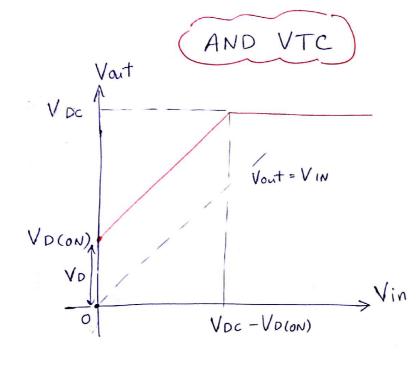

#### DIODE AND Gate

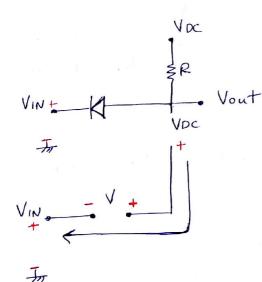

$$V \ge VD(ON) \rightarrow ON$$

$$V < VD(ON) \rightarrow Off$$

FIF V≥ VD(ON) then DIODE is ON

Any VIN ≤ VDC - VD(ON) at least one diode is ON

Vout = VD(ON) + VIN

La la output because la input

IR = VDC - VOUT = VDC - VD - VIN

R

### \* Truth Table

| A | В | olp |

|---|---|-----|

| L | L | L   |

| L | Н | L   |

| H | L | L   |

| H | H | H   |

III V < Vp (ON) then DIODE is OFF

VDC - VIN < VD (ON)

Any VIN > Voc - Vo (ON) => high input

Vout = Voc > high output

IR = 0

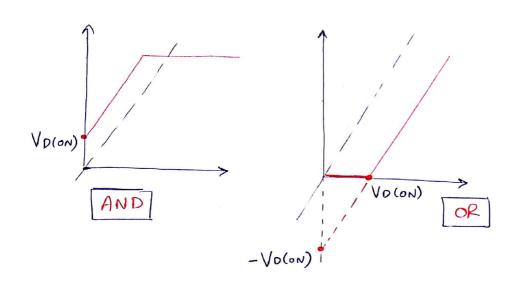

$$Slope = \frac{\Delta Vout}{\Delta Vin}$$

$$= \frac{Voc - Vo}{Voc - Vo - o}$$

$$= |$$

out => 3 letters like AND

Vout = VD(ON) + VIN

when diode is at VIN = 0, Vout = VD

at Vout = VDC -> VIN = VDC - VD(ON)

Any VIN > VO (ON) CORRESPONDING

X

Vout =

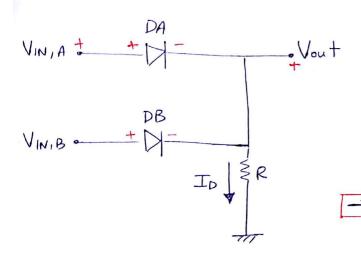

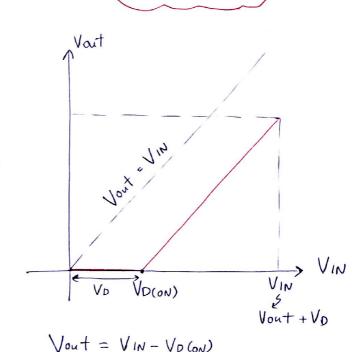

$$V_{IN} - V_{D}(ON)$$

input high  $\longrightarrow$  output high

$I_{R} = \frac{V_{OUT}}{R} = \frac{V_{IN} - V_{D}(ON)}{R}$

| • | Truth | Table | OR GAT | 1 |

|---|-------|-------|--------|---|

|   | A     | В     | 0/p    |   |

|   | L     | L     | L      |   |

|   | L     | Н     | Н      |   |

|   | Н     | L     | Н      |   |

|   | Н     | Н     | Н      |   |

|   |       |       | '      |   |

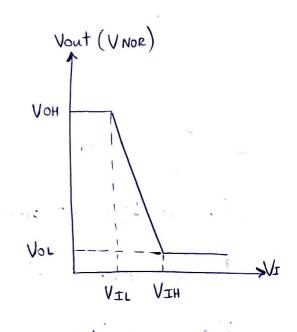

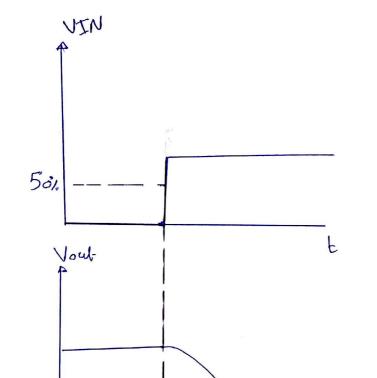

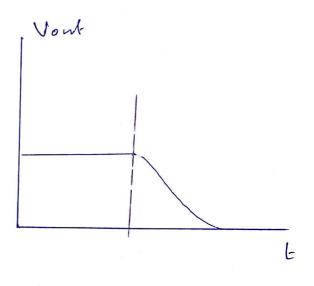

VTC

OR

IN >2 letters like or

$$slope = \frac{Vout - O}{Vout + VO - VD} = 1$$

### DIGITAL ELECTRONICS

#### EX 2.3

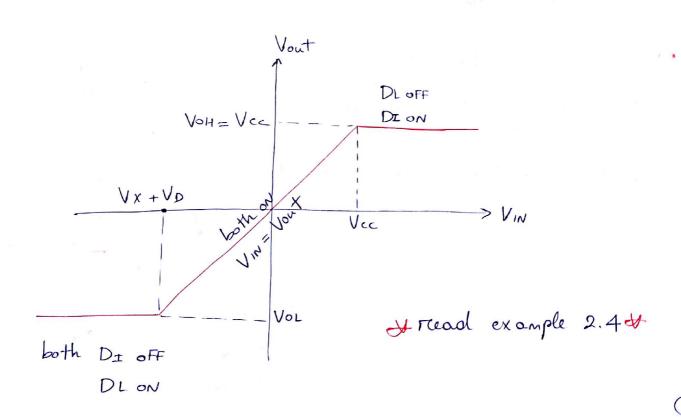

Diode-Resiston AND gate

Show that DA is off if VINA is 1 V higher then VINB. VD(ON) = 0.7 V

#### SOLUTION

Assume DA is on

Lassumption wrong

Assume DB is on and check for DA

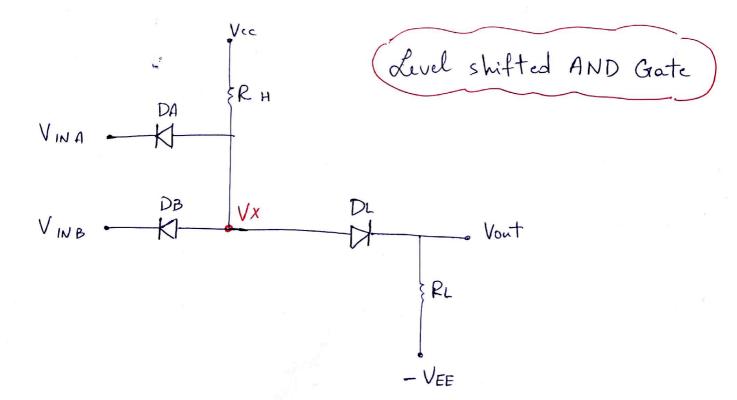

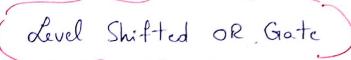

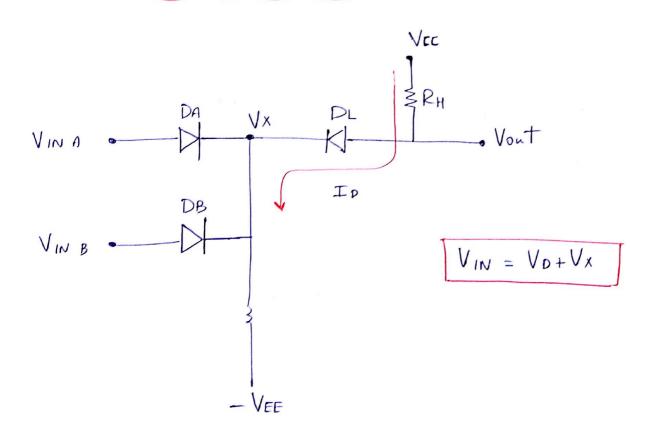

Degradation 1 - increase on decrease in o/p voltage compared to i/p. To remove degradation a level shifted diode is added.

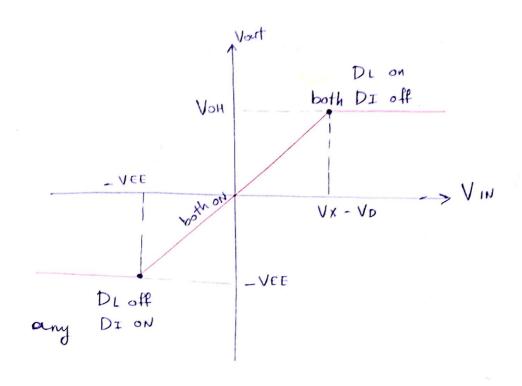

1 Any input low

VIN < VX - VD => corresponding diode is ON

$Vx = V_{IN} + V_{D}$

All inputs low

VIN < VD + VX >> both diodes are off

Vout = Vol = Vcc - IDRH = VDL(ON) + IDRH - VEE → independent of inpit

- 2) At least one input > Vx + VD -> corrresponding object is on

- 2.0 Vx < Vcc Va → DL is on Vout = Vin

- Vout = VoH = Vcc

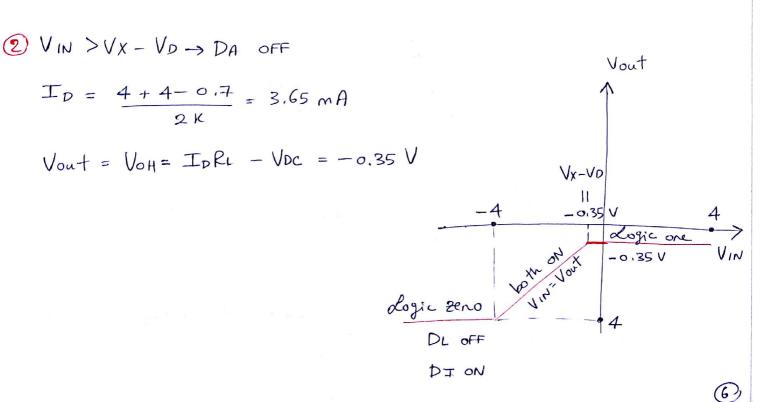

#### Problem 2.18 1-

#### Solution :-

### DIGITAL ELECTRONICS

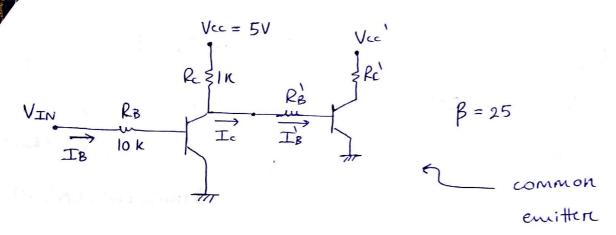

# CH. 4 Introduction to Bipolan Digital Circuits

# 4.1 Analysis for BJT

B

$$= I_{B}$$

$$I_{B}$$

$$I_{C} = I_{B} + (-I_{E})$$

$$I_{C} = (I + \beta_{R})I_{B}$$

### 1 Saturation mode

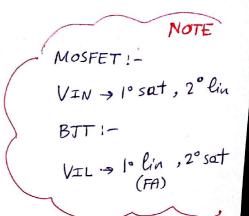

NOTE :-

ex 4.1

STANDARD VALUES

$$O' = \frac{I_c}{\beta I_B} = 0.137$$

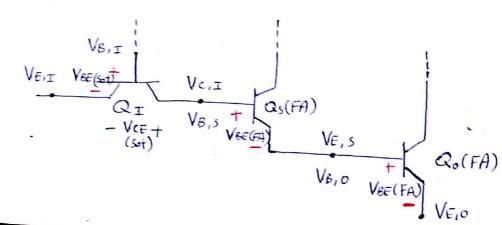

#### ex 4.2

Find voltage at each emitter and collector for all transistor

$$V_{E,I} = -V_{CE,I}$$

(sot) + 2  $V_{BE}(FA)$

= 1.2 $V$

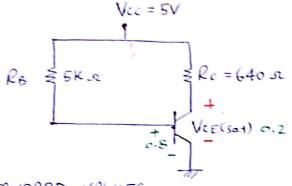

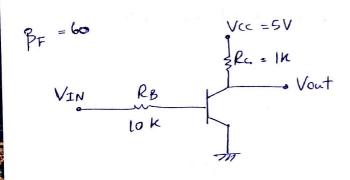

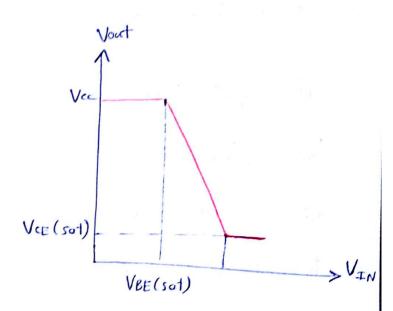

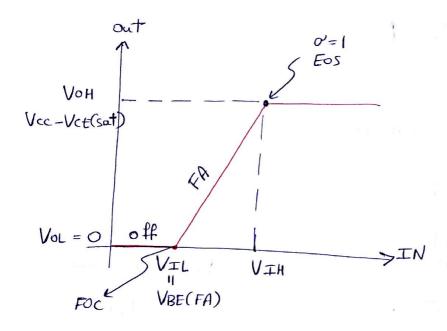

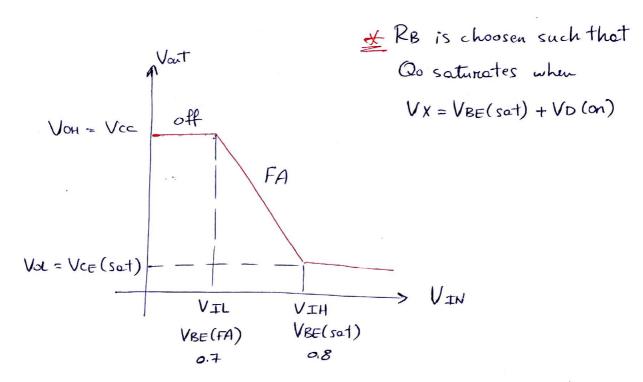

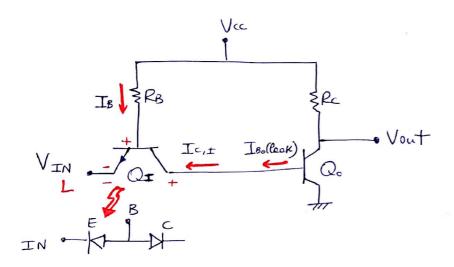

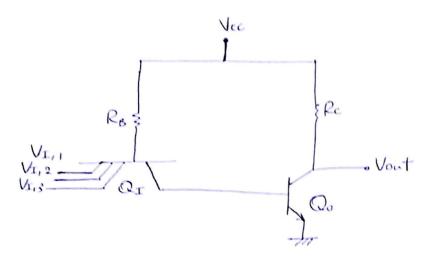

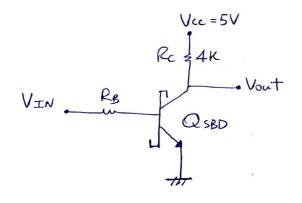

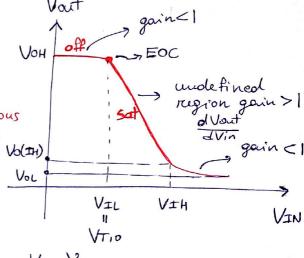

### 4.2 BJT- Inventer

VIN RB

Qo VCE

RE

TB(initially) = 0

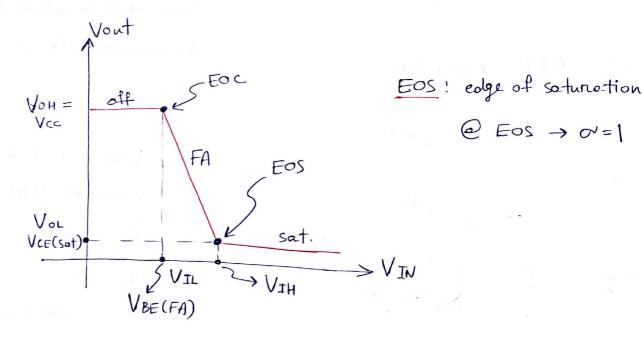

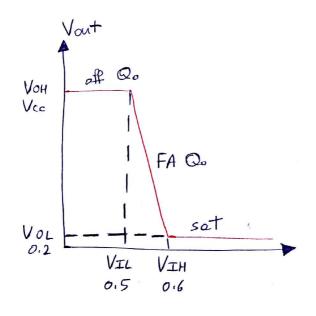

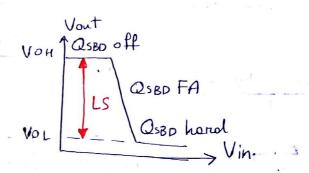

VIL -> from cut off to FA

VIH -> from FA to sat

- VOH -> Vont high

VIN < VBE (FA)

Qo is off

IRc = 0

- Vout = VOH = Vcc

- 2 VIN bow (VIL) input increases until Qo turns FA

\* VIL > input @ which Q turns (3)

As input increases IB increases -> Ic increases -> VRC increases

>> Vout = Vcc - VRC -> decreases.

- 3 Vout low (VOL)

input increases until Qo saturates

Vout = VOL = VCE(Sat)

- 4 VIN high (VIH)

Input at which Qo saturates

VOH, VOL, VIH, VIL: critical voltages

EOC: edge of constructance

BFRC.

$$T_{c}(Eos) = \frac{Vcc - VcE(sot)}{Rc}$$

$$V_{IH} = V_{BE}(sot) + \frac{Vcc - VcE(sot)}{R} * \frac{RB}{Rc}$$

$$T_{B} = \underline{Tc} = Vcc - VcE(sot)$$

Scanned by CamScanner

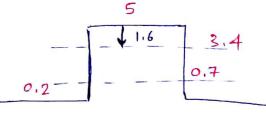

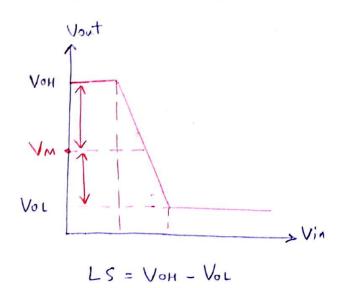

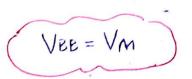

Noise Margins X

Safety margins for high and low voltage levels

VHNM = VOH-VIH (high noise margin) for logic I

VLNM = VIL-Vol (low noise margin) for logic 0

#### ex 4.4

VIL = 0.7

VOL = 0.2

VOH = 5V

VIH = 1.6 V

$$HNM = 5 - 1.6 = 3.4$$

$$LNM = 0.7 - 0.2 = 0.5$$

the higher noise mongin the better it is

i/p 0,7

- => @ high-state output of Qo con't be smaller than VIH so that the transistor of the next stage is able to saturate

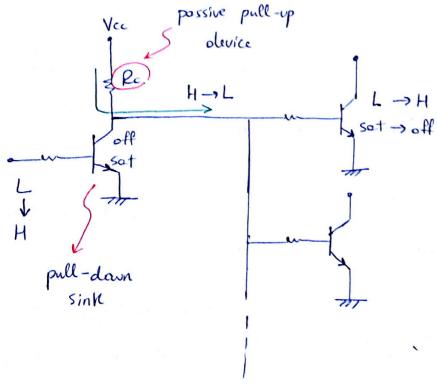

- 4.3 TTC cet block oliagram

- 4.4 Level shifting BJTs

4.5 Discharging Paths & Base driving circuits

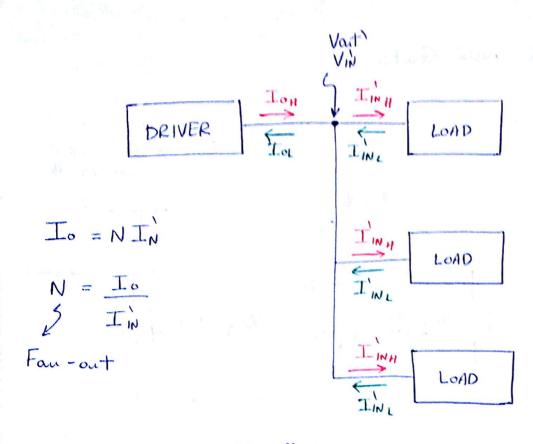

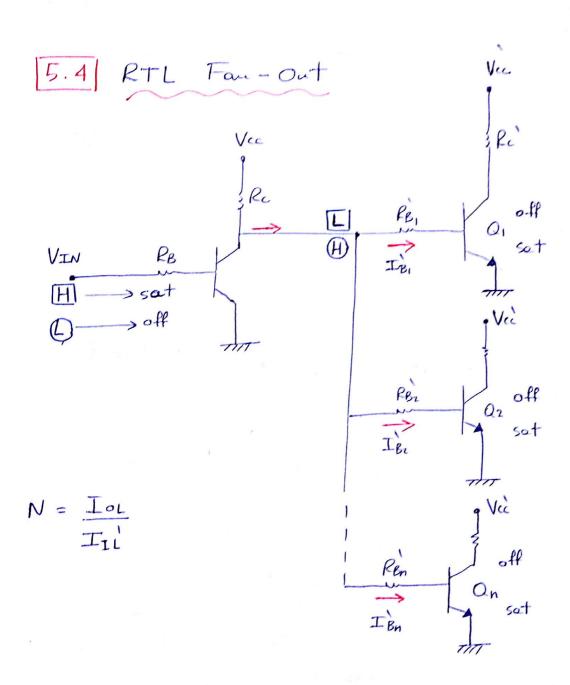

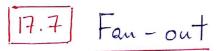

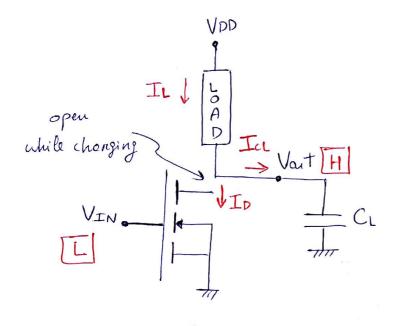

Fan-out & Fan-in

- € Fan out: is the max number of load gotes that can be connected to the o/p of a driver

- € Fau-In: is the number of inputs allowed at one gote.

ValentV

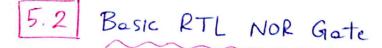

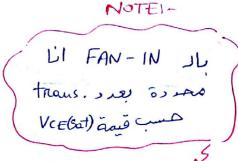

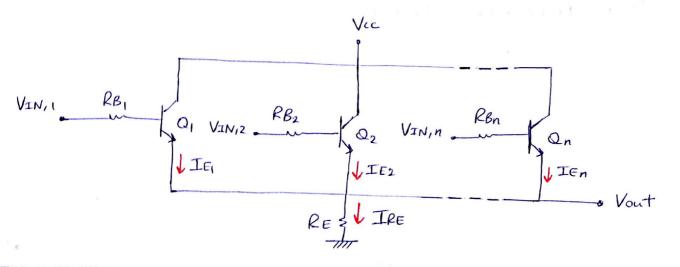

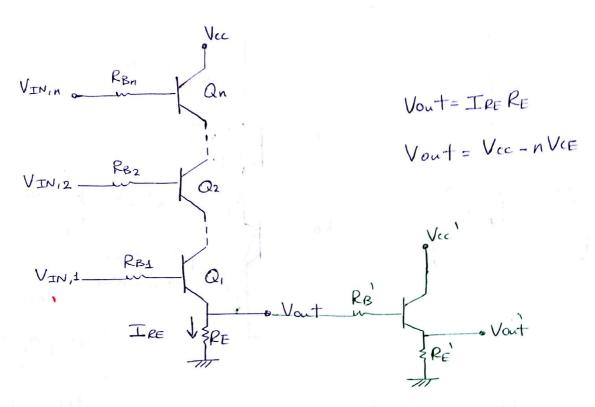

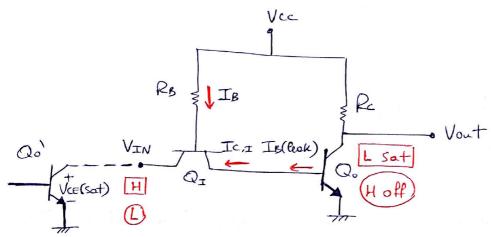

# CHAPTER 5 Resistor Transistor Logic RTL

$$I_{RC} = \sum_{i=1}^{n} I_{C,i} = I_{C,i} + I_{C2} + ... + I_{CN}$$

3 Any input low ore all inputs low

Both transistors are off

Q1 is saturating

for Q2 to turn FA

for Q28Q1 saturating

- D Any input low → BJT off Vont = Von = Vcc

- ② All inputs high → BJTs saturate Vout = n VcE(set)

VCE(sot) < VBE(FA)

</pre>

| IN, | IN <sub>2</sub> | Vout |

|-----|-----------------|------|

| 0   | 0               | 1    |

| 0   | ١.              | J    |

| 1   | 0               | 1    |

| 1   | l               | D    |

### Adogic Table (1)

|   | IN1 | IN <sub>2</sub> | IN3 | IN4 | Vout |

|---|-----|-----------------|-----|-----|------|

|   | 0   | 0               | 0   | 0   | 1    |

|   | 0   | 0               | 0   | ١   | 0    |

| - | 0   | 0               |     | 1   | 0    |

| _ | 0   | × į             | 1   |     | 0    |

|   | ١   | ı               | 1   | 1   | 0    |

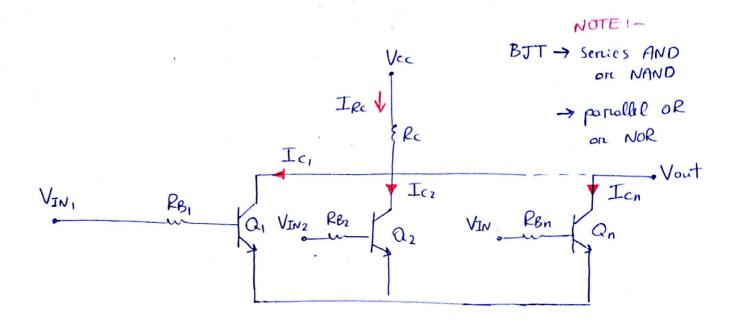

# 5.3 Basic RTL NAND Gate

=> Two inputs NAND Gate

VCE(sot) = 0.17 V, VBE(FA) = 0.7 V

=D

$$n \text{ VCE}(sot) < \text{VBE}(FA)$$

$n(0.17) < 0.7$

$n < \frac{0.7}{0.17} = 4.12$

$n = 4$

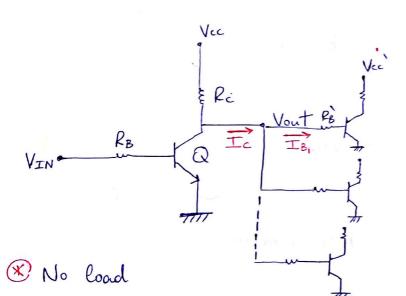

When olp of driver is high, load transistors saturate and current flows through RBS

→ o/p high is used to find Fan-out for RTL inventer

- current supplied through Rc, must be enough to saturate all load gate BJTs me no. of load gate are limited

- 3 To assure the saturation of load BJTs

$$V_{OH} = V_{IH}$$

$$= I_{B} R_{B} + V_{BE} (sat)$$

$$= \frac{I_{C}}{\beta} R_{B} + V_{BE} (sat)$$

$$= \frac{V_{CC} - V_{CE} (sat)}{\beta} R_{B} + V_{BE} (sat) \dots (1)$$

0 =1 @ Eos

load gates identical  $\Rightarrow I_{RB} = \frac{V_{OH} - V_{BE}(sat)}{P_{B}^{2}}$

$$N = \frac{I_{Rc}}{I_{RB}'} = \frac{V_{CC} - V_{OH}}{R_{C}} * \frac{R_{B}'}{V_{OH} - V_{BE}'(sat)} = \frac{V_{CC} - V_{OH}}{V_{OH} - V_{BE}'(sat)} * \frac{R_{B}'}{R_{C}}$$

### DIGITAL ELECTRONICS

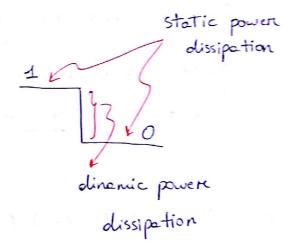

# 5.5 RTL Power Dissipation

OH PCC (OH)

$$Icc = IRC = \sum_{i=1}^{N} I_{B,i}^{i}$$

$$IRC = NI_{B}^{i}$$

Scanned by CamScanner

$$IRc \left( 1 + N \frac{Rc}{PB} \right) = \frac{V(c - VBE (sat))}{PB}$$

$\Rightarrow eq. \square$

average powere dissipation

SOL

$$Icc (OL) = \frac{Vcc - VcE(sat)}{Rc}$$

$$=\frac{5-0.2}{1 \text{ K}}=4.8 \text{ mA}$$

$$Icc (OH) = \frac{Vcc - VBE (Sat)}{Pc + \frac{PB}{N}} = \frac{5 - 0.8}{1K + \frac{10K}{1}} = 382 VA$$

$$Pcc (avg) = \frac{4.8m + 0.382m}{2} * 5 = 12.96 mW$$

when load 1 -> Pcc 1

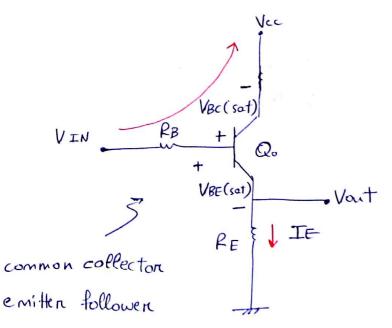

### 5.6 Besic RTL non-inventer

when VIN < VBE(FA)

Qo is off

IE = 0

Vout = 0 = Vol

At VIN = VIL = VBE (FA)

BJT turns on (FA)

\*As input increoses beyond VIL = VBE (FA),

IB 8 IE increose Vout = IERE increoses

\*Input Keeps increasing until a saturates

Vout = VoH = Vcc - VCE (sat)

VIII when Q turens sort

VIN > VCC

$$CX$$

5.4  $Vcc = 5V$ ,  $RB = 10K$   $RE = 1K$ ,  $B_F = 25$ ,  $Vol = 0$

$$VIL = 0.7$$

,  $Voh = 4.8 V$ ,  $VIH = 7.4 V > Vcc (from eq. 21)$

$$Q saturcates$$

$$Vout = Voh = Vcc - Vce (sat)$$

# 5.7 Basic RTL "OR" & "NOR"

In general

- All inputs low

All BTTs are low

Vout = 0 = Vol

- 2 Any on all inputs high

corrresponding BJT saturates

Vout = Vcc VcE(sat) = VoH

| ļ | IN1 | IN2 | IN3 | out |

|---|-----|-----|-----|-----|

|   | 0   | 0   | 0   | 0   |

|   | 0   | 0   | 1   | 1   |

|   | 0   | l   | 7   | 1   |

|   | 1   |     | 1   | 1   |

$$\Rightarrow \pm_{B=} \underline{\perp_{E}}$$

$$\beta_{F} + 1$$

### DIGITAL ELECTRONICS

### # AND Gate

Any on All inputs low corresponding Q is off, also all other Q are off IRE = O Vout = 0 = Vol

| 1 | IN | IN <sub>2</sub> | Out |  |

|---|----|-----------------|-----|--|

|   | 0  | 0               | 0   |  |

|   | 0  | 1               | 0   |  |

|   | l  | 0               | 0   |  |

|   | 1  | 1               | . 1 |  |

- 2 Both inputs high For a 2-input AND Grate

- When Q2 is FA, Q1 sat.

Vont=Vcc VcE,2(FA) VcE,1 (sat)

- ¥ when both soturate Vont=Vcc - 2 VcE(sat)

- >if for n-inputs all as saturate VOH = VCC - nVCE(sat) > VIH

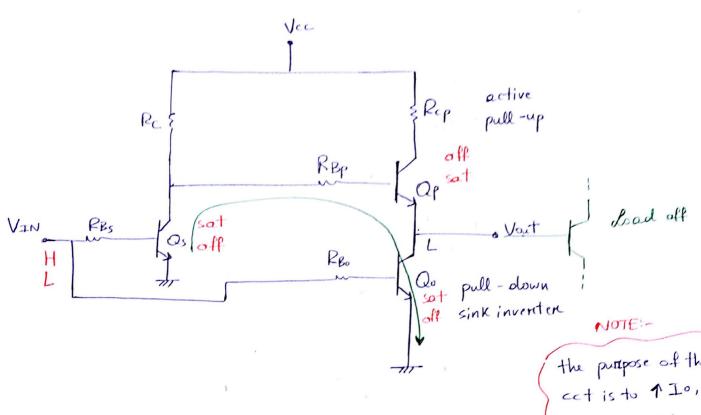

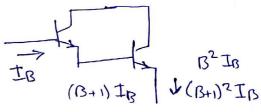

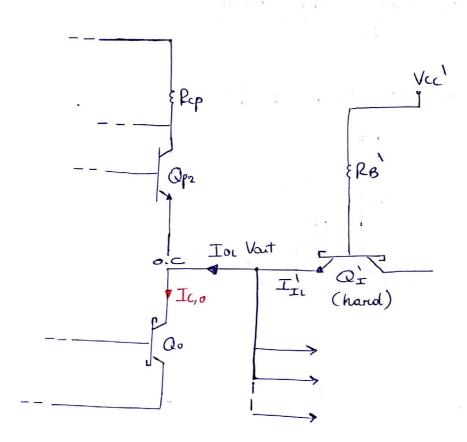

# [5.8] RTL with active pull-up

A Rap ≈ O.IRc for obsign

→ more sourcing current & high four-out

\* RBs = RBo = RB and Qs & Qo operate at the same time

≠ if VIN is high, as & Qo saturate Voit = Vo = VcE, o (sat)

-VCErs(sat) + IBP RBP + VBE, P + VCEro(sat) =0  $I_{BP} = \frac{-V_{EP}}{R_{BP}} \Rightarrow negative \Rightarrow Q_P \text{ off}$

# if VIN is low, VIN < VBE (FA) > Os & Qo are off Vout = VOH = VCC - Icp Rcp - VCE,p (sat)

the purpose of this cct is to 1 Io, so FAN-OUT 1 too

why Qo is sink & as is not? for the exam

FAN-001

for low o/p at driver, load gates will be off and I in will be zero > ear't use for for-out calculations.

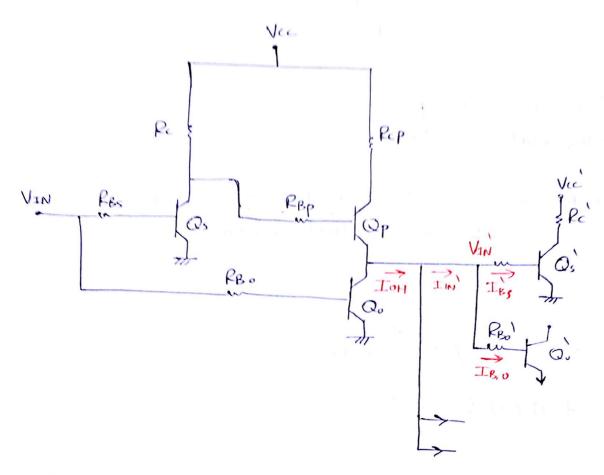

\* VOH = VIH to ensure saturation of load gates BJTs

$$V_{OH} = V_{IH}^{'} = I_{B}^{'} R_{B}^{'} + V_{BE}^{'}(sat)$$

$$= \frac{V_{CC}^{'} - V_{CE}^{'}(sat)}{\beta} \frac{R_{B}^{'}}{R_{C}^{'}} + V_{BE}^{'}(sat)$$

for simplicity ignore IBp.

$$\frac{V_{CC} - V_{CE,p}(sat) - V_{OH}}{R_{CP}} = 2N \frac{V_{OH} - V_{BE}(sat)}{R_{B}}$$

$$N = \frac{Vcc - VcE(sct) - Vout}{Vout - VBE'(sat)} \frac{RB'}{2Rcp}$$

Since Rep << Re => four-out for RTL with active pull is higher than that of basic RTL inverter

chap.5

$$\Rightarrow$$

5.11 /5.32/5.40/5.17

chap 4  $\Rightarrow$  4.12/4.20/4.3

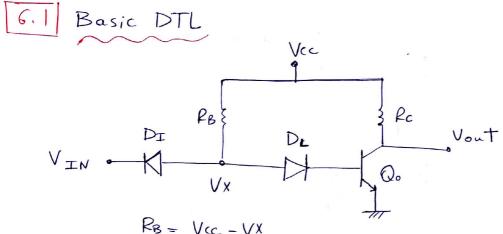

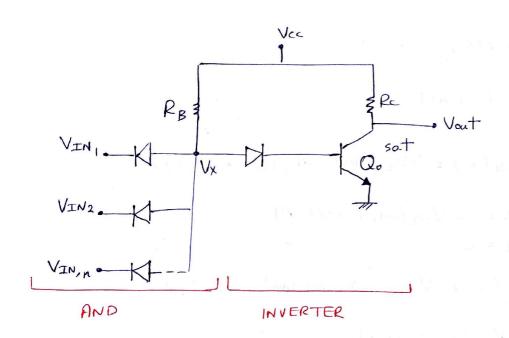

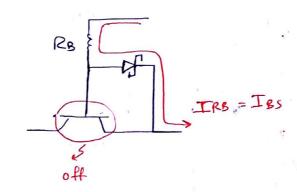

# CHAPTER 6 Diode Transiston Logic (DTL)

RB = VCC - VX

for RB design >> V between Vcc & VX

must be < than V between VX & VIN

- following analysis: VIN<VX

DL is off

VIL -> DL & Qo are on

when

$$V_X = V_{IN} + V_{DI}(on) = V_{DI}(on) + V_{BE,o}(FA)$$

$V_{IN} = V_{IL} = V_{BE}(FA)$

### DIGITAL ELECTRONICS

### \* For basic DTL

# \* Basic DTL NAND Grate

| L  | L | Н |

|----|---|---|

| Ĺ  | Н | H |

| H  | L | H |

| 14 | Н | L |

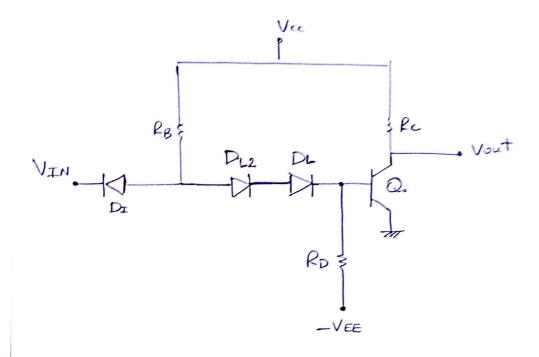

# 6.2 Modified DTL => Additional level shifting

the addition of a level shif diode, increases VIL > LNM increased

\* RD 8 - VEE are used as discharge paths

2

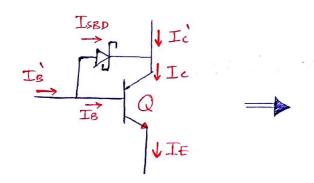

6.3 Transistor Modifical DTL

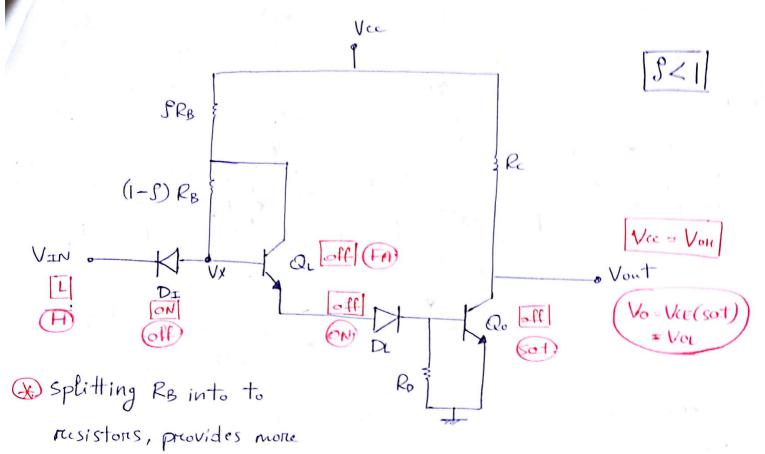

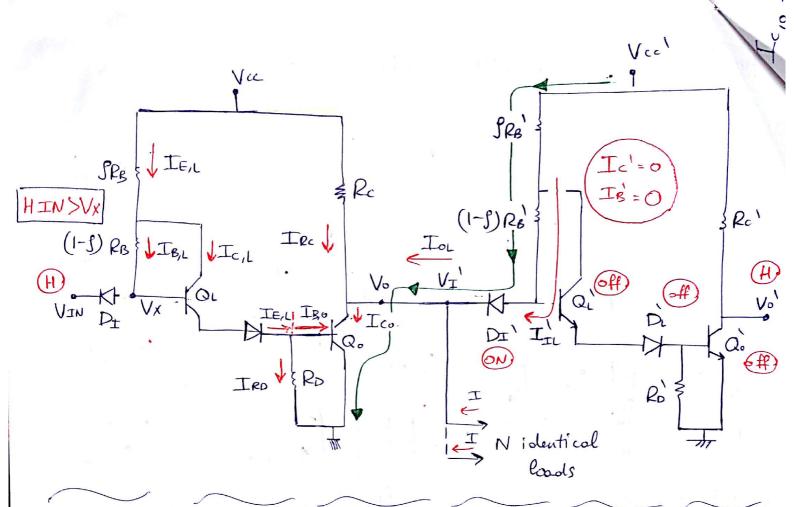

for load in IL state >> SRB+(1-5)PB = PB

For QL when ON, we have a voltage drop on  $(1-S)RB \gg Vc, L > VB, L$   $VBC, L = VB, L - Vc, L \Rightarrow negative$  BC junction is reverse biase  $\Rightarrow QL$  FA (does not saturate)

#### EXAMPLE 6.1

Driven: Current through

$$\int R_B \Rightarrow I_{SRB} \uparrow$$

,  $I_{E,L} \uparrow$

$$I_{B,o} \uparrow$$

,  $I_{C,o} \uparrow$ ,  $I_{OL} \uparrow$

$$N = I_{OL} \uparrow$$

$$I_{II}$$

#### DIGITAL ELECTRONICS

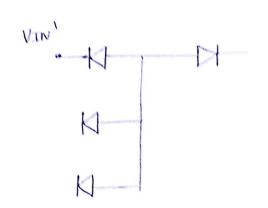

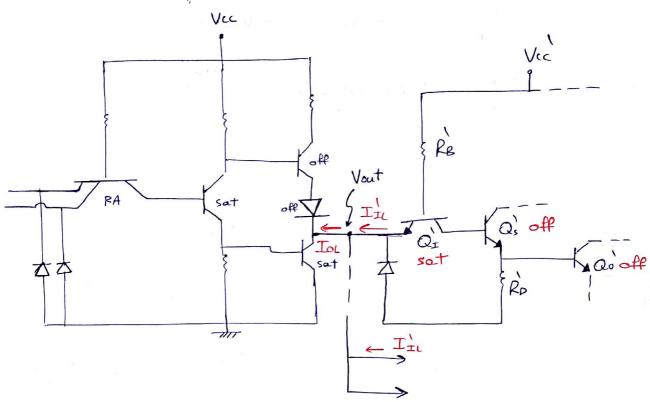

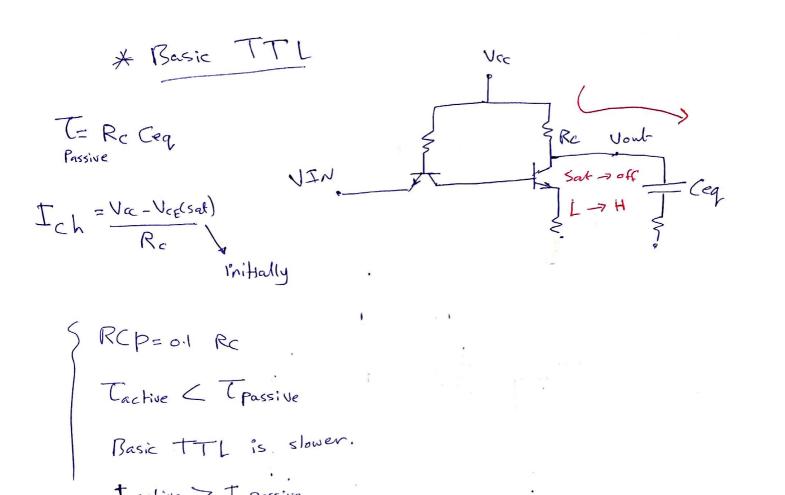

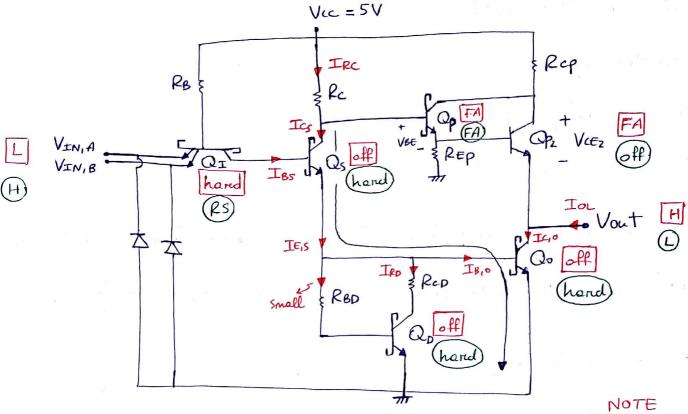

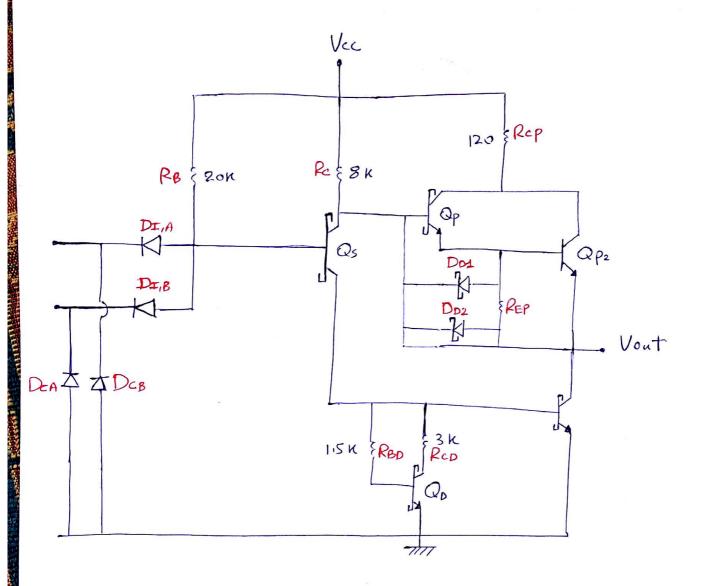

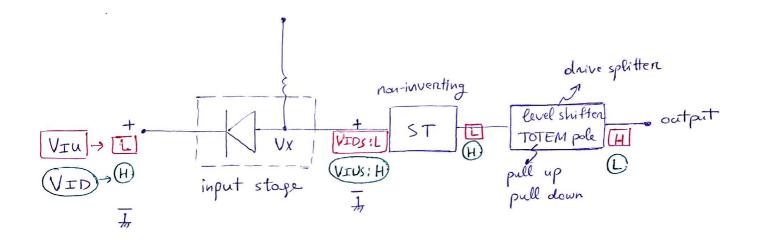

\* Chapter 7 Transistor Transistor Logic

7.11 Basic TTL inventer

→ Advantages: -→ Smaller size

→ higher fan-out

$$V_{B,I} > V_{E,I}$$

$$T_B = V_{CC} - V_{BE,I}(sat) - V_{IN}(low)$$

in MA

VIN (law) & VIL Elogic Zero (@ ECC)

then IB, I >> Ic, I

Q1 operates in a Kind of unconventional way:at "low input (B-E) T is Forward-Biased,

IB1 enters QI and IEI exits EI to low input.

This transiston action forces Ic, I into QI

But Ic, I = IBo (leakage) and is less than IB, I

Oo is off woltage at base is not enough to turn Qo on.

$$VIL = 0.7 - 0.2 = 0.5 V$$

Until now, VE, I < VB, I and Q I is in saturation region while input increases

As input increases, VE, I

becomes higher than VB, I

(B-E) T for Q = is reverse

blased, with (B-C) T still

forward blased > Q =

operates in RA region,

supplying large current to

Qo and Qo will still

saturate.

#### 7.2 Comparison of stored charge removal between DTL

#### and Basic TTL circuit

For TTL

B-C: 0.6 B-E: 0.8

$$V_{B,I} = V_{BE,I}(?) + V_{IN}(low)$$

=  $V_{BE,I}(?) + V_{CE}(sat)$

Ic, I: charge removal current for Q.

$$I_{scr} = I_{RD} = \frac{V_{BE,o}(sot)}{R_D}$$

⇒ Delay time of DTL is biggen, and TTL is faster.

EX 7.1 Find factor of improvement comparing TTL & DTL RD = 5K, RB = 2K, Vic = 5, BF = 50

$$I_{C_{\pm}/SCR}(TTL) = 50 \left(\frac{5-0.7-0.2}{2K}\right) = 102.5 \text{ mA}$$

#### 3 Basic TTL NAND Gote

with multi-emitten inputs

# (B-E) T forward, QI sot, Qo off Vo = Vcc = VoH

(2) All inputs high

(B-E) T revenuse biased, QI is RA

large current is supplied to Qo & Qo is sait

Vol = VCE (sat)

\* Fore two inputs: -

| Ι, | 工2 | Olp |

|----|----|-----|

| L  | L  | Н   |

| L  | H  | Н   |

| Н  | L  | Н   |

| Н  | Н  | L   |

NAND

#### DIGITAL ELECTRONICS

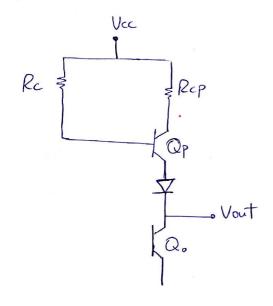

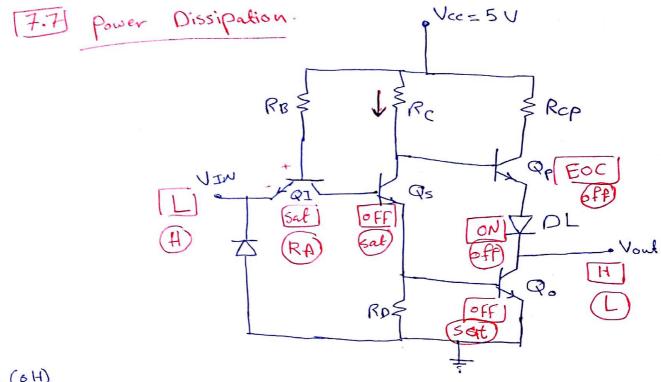

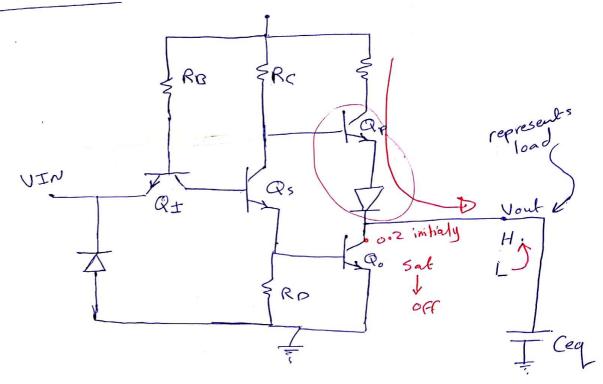

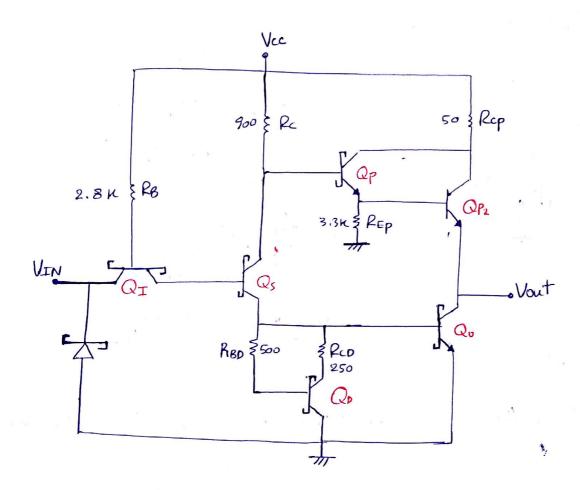

# Standard TTL NAND Gate with TOTEM Output

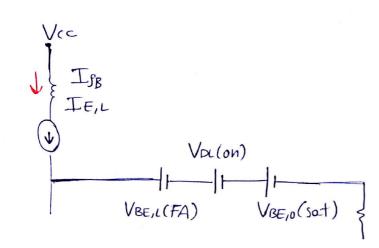

when QI,Qs sat & Qp is off

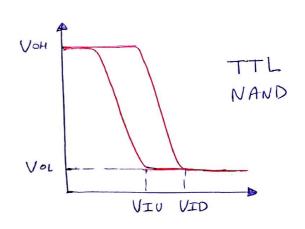

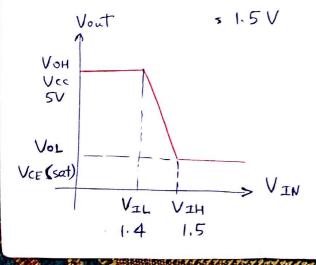

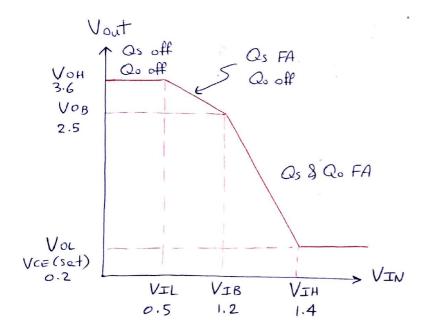

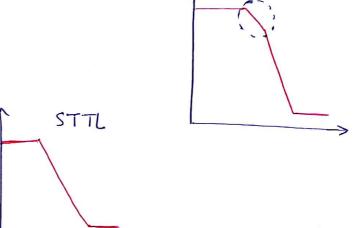

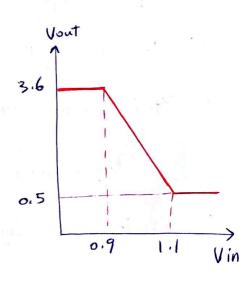

### 7.5 Standard TTL VTC

₹ Voh

Input low

high enough to saturate QI

IB, P(FA) ignored

VIL voltage at which as turns FA

Ic,s & IRC

VIB break input voltage when Qo is also FA

Vos break output voltage

thun IE,s & IRD & IB, P (FA) ignored

#### NOTE

without RD → there isn't a break voltage

→

$$V_{OB} = V_{CC} - \frac{V_{BE,o}(FA)}{R_{O}} R_{C} - V_{BE,p}(FA) - V_{OL}(ON)$$

$$VOB = VCC - \left(\frac{RC}{RD} - I\right) VBE(FA) - VDL(ON) = 2.5 V$$

$$V_{IH} = 2V_{BE}(sot) - V_{CE,I}(sot)$$

$$= 1.4 V$$

$$V_{OL} = V_{CE,o}(sat) = 0.2 V$$

As input increases and both Qo & Qs are FA, output goes down faster with a steeper slope of the VTC is high enough to saturate both Qo & Qs.

الاحين ٤٦/١١/٢٤

Small

negled

Tecp neglect (small)

$$I_{cc}(oL) = I_{RB}(oL) + I_{Rc}(oL)$$

.

$P_{cc}(aug) = I_{cc}(oL) + I_{cc}(oH)$   $V_{cc}$

Same circuit but smaller current = higher resistance values.

- advantage: less power dissuportion.

dissadvantages: less for out.

\* Example 7.5

Pacaug) 919 MW Company them when we change the resistance.

but in example 7.4 Pacaug) = 10.4 mW

# [7.10] High speed TTL

higher current, less R values advantages: higher speed and better Fan-out. disadvantages: worse power dissapation.

to have higher current = 1-less R values

2 Also ap and DL ours replaced by

Dowlington pair.

# Back to 7.4

Comparison of load capacitance charging between basic TTL and TTL with TOTEM Pale.

\* TOTEM Pole.

Qo Sat -> OFF

OIP L -> H

T = Rep (eq.

Ich. = Vcc - Veep - VPL - Vee, o (sat)

Rep

=> TTL with ToTEM Pole is fasten than Basic TTL.

#### DIGITAL ELECTRONICS

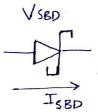

(\*) Chapter 8 Schottkey Transistor Transistor Logic (TTL)

VSBD : shottley barrier diode

\* SBD turns on at VSBD = 0.3 V

\* Shottkey Clamped BJT

-> For regular BJT: -

VBC (sat) = VBE (sat) - VCE(sat)

-DTo avoid saturation an SDB is connected in parallel with the (B-C) JN of BJT

- IB increases until SBD turns on at 0.3 V -> Diverting wherent through SBD, and clamping (B-C) voltage at 0.3 V

- -> BJT is prevented from saturating because VSBD < VBC (sat)

- SBJT is said to operate in hard mode (some refrences call it EOS)

- -DADVATAGES: provides less time spent in discharging saturation current when transistor turns from sat to off

#### \* Modes of operation

1 Cut off

Small current, such that both SBD and BJT are off:  $T_B' = T_C' = T_E = 0$

2 FA mode

(B-E) JN → forward biased VB>VE (B-C) JN → reverse biased VB<VC, SBD off

like a BJT in FA VBE(FA)=0.7

3 Hard mode

BE & BC junctions are forward, with (B-C) voltage clamped at VSBD (0,3 V).

VBE (hard) = 0.8 V, VEC (hard) = VSBD (hard) = 0.3 V

VCE (hand) = 0.5 V , Ic(hand) = BIB (hand)

Ic' (hard) = Ic - ISBD = BIB - ISBD

### 4 Reverse - Shottkey mode

VBC can't reach 0.7 V => BJT con't be RA (for a BJT to RA

$$I_{B} = I_{C} = I_{E} = 0 \rightarrow BJT$$

is off

find the logic swing

# <u>≯</u> [Voн]

Input high enough for QSBD to operate in hand mode

# 8.3 Shottkey - Clamped TTL (STTL)

Qp & Qpz: Darlington pair

> To provide higher current

REP: Discharge path for Qp2

apr con't saturate -> no need to asso

VCEpz = VBE, pz (FA) + VCE, p(hand)

= 0.7 + 0.5

= 1.2 V > VcE (hand)

→ Qp2 → FA mode

\* Ro in TTL is replaced by Qo

RBD & RcD : Dischange paths for Qo

\* RBD & RCD are designed such that Qo & Qo run simultaneously

\* Ps won't operate unless, Qo & Qp are on

- Removes break point

- → VTC sharper (less transition width)

- Faster then TTL

- Better noise margin

TT

### 8.3 Shottkey - Clamped TTL (STTL)

\* When apr is on, if apis in (saturation)

VCE, p2 = VCEp(sat) + VBE, p2 > VCE (sat)

⇒ apr does not saturate -> no need for a asbo

\* Op is always ON

Qs: logic invension drive splitter

\* Qs turs on only when Qo & Qo are ON

is very small

IBD< ICD

ignore

Removal of break point

- 1 Lower VIH (compared to TTL)

- 2 Betten HNM

- 3 Less transition width

Fasten by 8 ns

for STTL delay = 2 ns

QD: active discharge path for Qo when Qo turns from hand to off

REP: connection path for Qo to ground discharge path for Qp2

ex 8.2 SSTL VTC

. input low

- when Qo, Qs turn FA

\* input high

-> when Qo, Qs turn hand

VOL = VCE, (hard) = 0.5

#### 8.4 STTL Fan-out (output low at driver)

neglect ISBD (Small)

see the wherents

> go back to page 1 to

because

$$\Rightarrow$$

$N = \frac{IoL}{I'L}$

#### \* Icc (OL)

ignore FA Bose unnents

#### 8.6 Low Power STTL

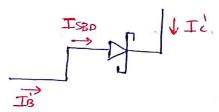

Z QI is replaced by DIAS DIB since QI in regular TTL was used as a discharge path for base curinent from Qs, when it switches from saturation to off.

FOR STIL Qs does not saturate > no need for QI

\* For output low -> Qp currents are ignored.

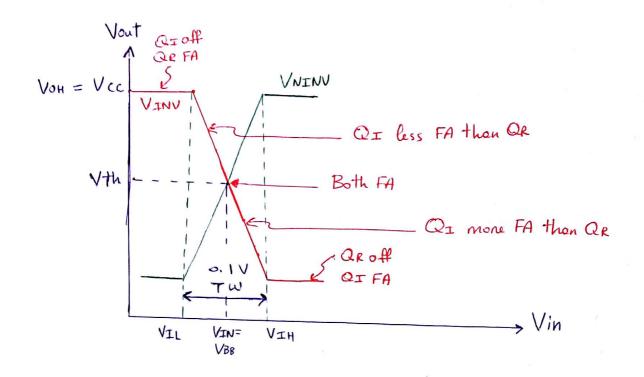

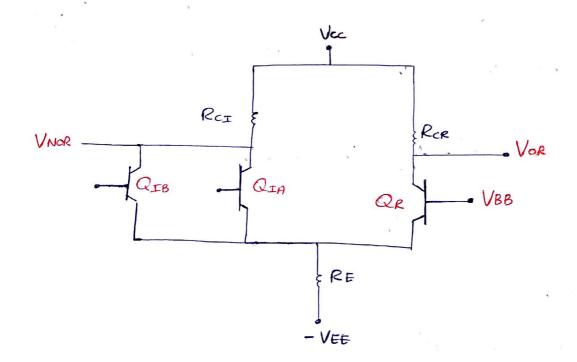

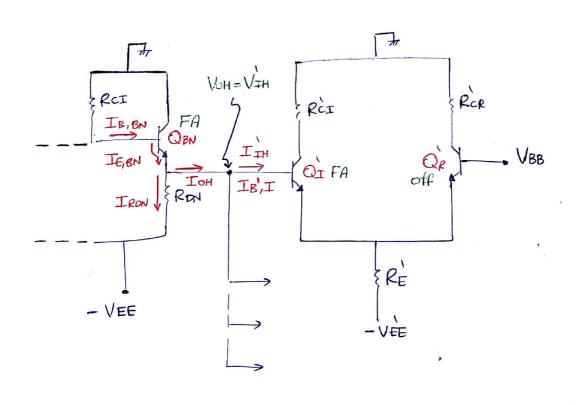

# CH. 11 Baséc Emitter Coupled Logic (ECL)

# 11.1 Basic BJT Current Switch

→ Ignone Bose currents

\*Ic & IRE (if one of the transistor is on and the other is OFF)

\* Ic = IFE (if both are ON)

→ Outputs: -

VINV = VC,I = VCC - ICI RCI

VNINV = VC,R = VCC - ICR RCR

With proper selection of RCI and RCR, VIN = VINV = VTH = VBB

Input low and high voltages VIL, VIH

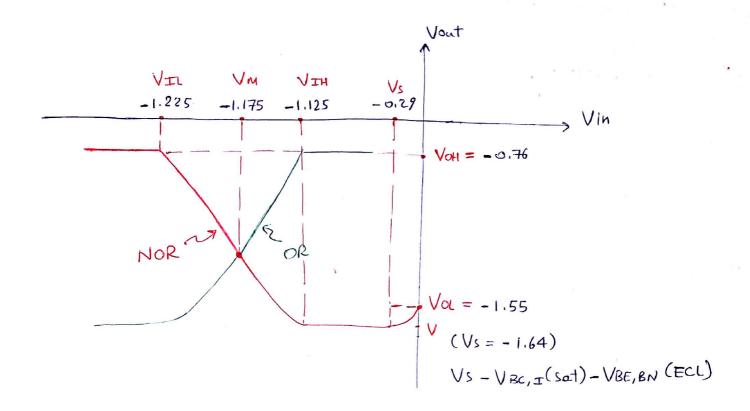

By experimentation, transistion width (Tw) equal 0.1 V

VIL = VBB - 0.05 V

VIH = VBB + 0.05 V

but Qr has more current than QI

When VBB < VIN < VIH, both Q's were on but QI has more current than Qr

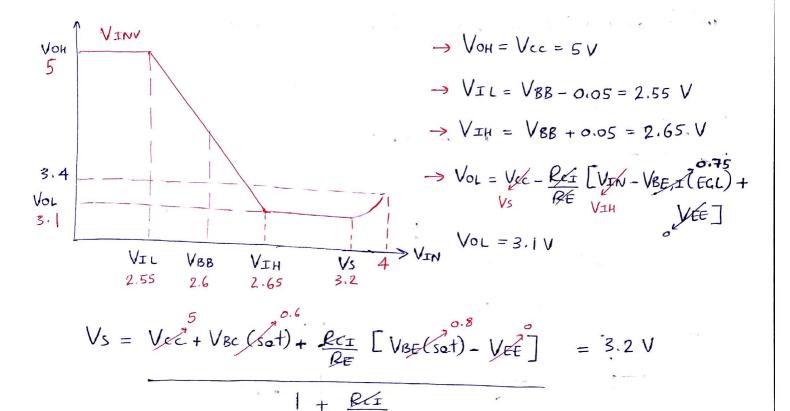

\* VOL (output low voltage)

QI is on

=> QR is off

Vs = VIN when QI saturates

$$Vs = Vcc + VBc (sat) + \frac{RcI}{RE} (VBE (sat) - VEE)$$

$$1 + \frac{RsI}{RE}$$

#### DIGITAL ELECTRONICS

EX 11.1 Find critical voltages Vcc = 5V, -VEE = gnol = 0 VBB = 2.6V, RCI = RCR = RE = 1K, VBE(ECL) = 0.75V VBc(sat) = 0.6V

QR has fixed input at Base ⇒ does not saturate

#### \* ADVATAGES OF ECL Switch

- I dow sensitivity to noise because of the differential nature of the circuit

- 2 Current drawn from power supply is constant during switching

- 3. O/p is referenced to Vcc, and if Vcc is replaced with ground with decruesing VEE, o/p will be more stable.

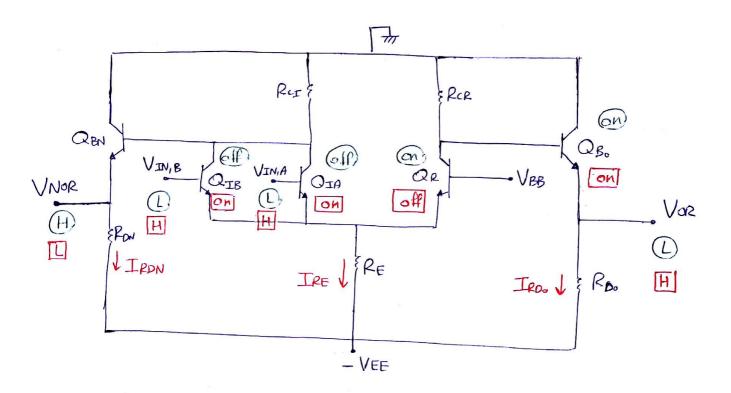

#### 11.4 Basic ECL NORIOR Gate

\* Any input high

Conrusponding QI is on, current flows in RCI, QR is off

VNOR low, Vor high

\* All inputs low

QI's are off, QR is on, IRCI = 0

V NOR high, Vor low

| A   | В        | NOR | OR    |

|-----|----------|-----|-------|

| 0   | 0        | 1   | 0     |

| 0   | 1        | 0   | 1     |

| 1   | ò        | 0   | . 1 . |

| 1-1 | 1 1 to 1 | 0   | . (   |

11.5 MECLI NOR/OR Gate with Buffens

More The Teat I and T

-> Buffers 1- QBN, QBO olway FA

\* Provide high ofp current and low ofp resistance - FAN-OUT high

\* High switching capability

\* o/p at current shitch is level shifted by VBE, BN (ECL) : so that inputs 8 outputs are compatible

## DISADVANTAGES

- -> High power olissipation

- Jorge current spikes, with the dereased switching time Ly Vcc is replaced by GND, and power supplies NOR H 8 OR L buffers are isolated from rest of the circuit

11.6 MECLI Voltage Transferi ch.

(1+BF)IB, BN

Like for writert switch

VIH = VBB + 0.05

\* Vol input high QI on, QR off

\* Vs when QI saturates

Noise sensitivity :- quantifies the effects of input variations

Noise immunity: - sensitivity

logic swing

$$NIH = \frac{NSH}{LS}$$

ex 11.2 Find LS, noise margins, noise immunities

$$V_{IL} = -1.225 \, V$$

,  $V_{IH} = -1.125 \, V$ ,  $V_{S} = -0.29 \, V$

$$\rightarrow NIH = \frac{-0.76 - -1.175}{0.79} = 0.53 \text{ V}$$

$$\rightarrow NIL = \frac{-1.175 - -1.55}{0.79} = 0.475 \text{ V}$$

### 11.7 MECLI Fan-out

Output at NOR Driver, input at QI'

During low input, no current in Qi ⇒ fau-out ≈ ∞ not acceptable

$$I'_{IH} = I_{B,I} = I_{F,I}$$

$$\beta_{F+1}$$

→ Unlike TTL, where drivers of sink the load current, and thus does not affect the outputs voltage, the ECL load drags current from the ECL's driver, which decreases the drivers output voltage → voltage at output of driver must be kept at Von

### 11.8 MECL Power Dissipation

Input low

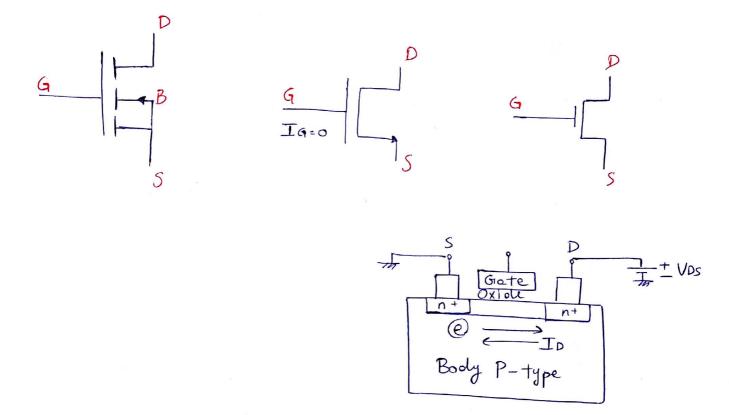

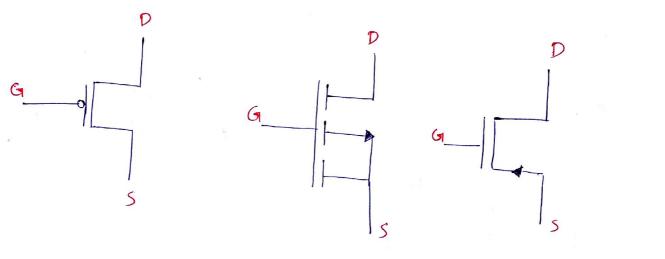

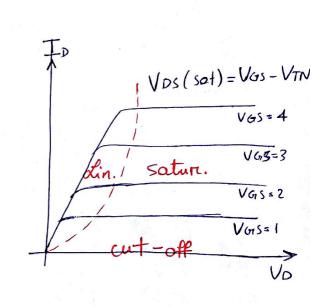

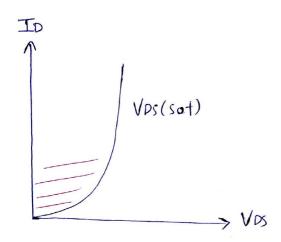

## CH. 16 Metal Oxide Semiconoluctor FET N-channel MOSFET

16.3 Modes of operation

N- CHANNEL

P- CHANNEL

\* N-channel

Thrushold Voltage

VGS > VTN, VDS > 0 for current to flow from obtain to source

1 Cut - off

Vas< VTN , ID=0

2 Linear mode

VGIS > VTN, VDS < VDS (set) VDS < VGS - VTN

lion

ID (lin) = K [(VGS-VTN) \* VDS - VDS<sup>2</sup>], M: transconductance parameter

3 Saturation mode

VGS > VTN

Vos > Vos (sot)

VOS > VGS - VTN

$ID(sot) = \frac{K}{2} (VGS - VTN)^2$

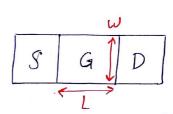

# 16.4 MOSFET Transconductance

$$K' = \mathcal{J} Cox^{1}$$

$$Cox' = \frac{Cox}{tox}$$

### enhancement: VTN+W

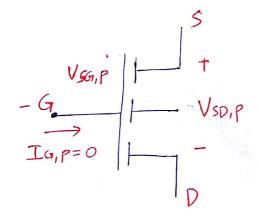

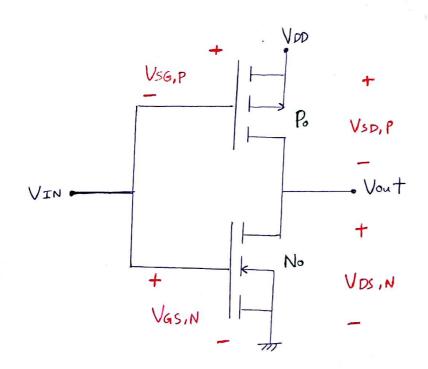

## 16.6 P- channel MOSFET

2) Linear mode

$$VsG,P \ge -VT,P$$

3 Saturation mode

$$I_{P,P}(set) = \frac{k}{2}(V_{SG,P} + V_{T,P})^2$$

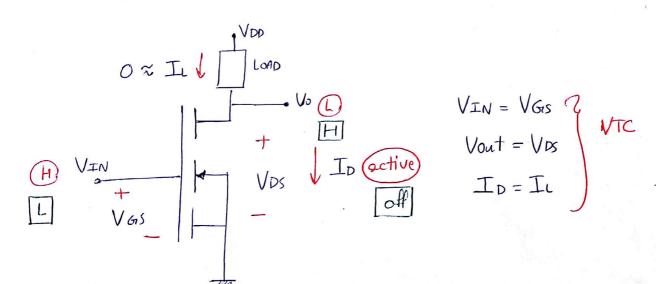

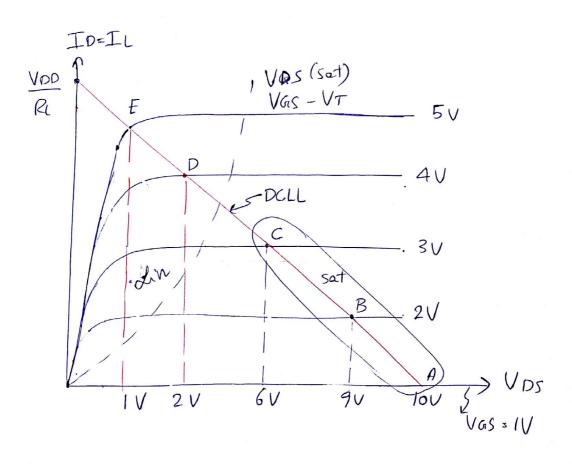

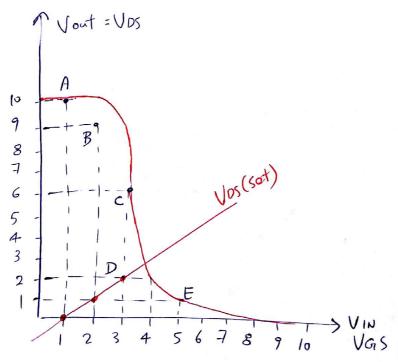

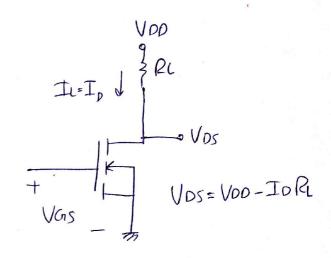

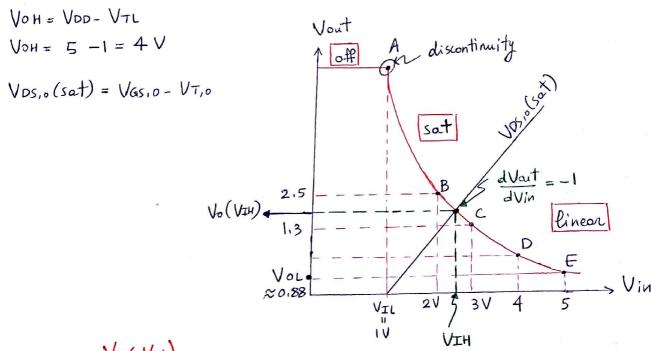

CH. 17 Introduction to MOSFET Digital Cinuits

Greneral NMOS inventor

## 17.2 Zero Drain Current active MOSFET

## ▶ Analytically • ◄

$$ID(lin) = K [(VGS - VTN) VDS - \frac{VDS^2}{2}]$$

$$O = K [$$

VDS > 2 VDS(set) does not apply

$$RDS = \frac{dVDS}{dID}$$

$$\frac{dID}{dVds} = R \left[ (VGIS - VTN) - VDS \right]$$

$$|R_{DS}|$$

=  $\frac{1}{40 \, \text{M}[(5-1)-3]} = 25 \, \text{K.S.}$

$$|R_{DS}| = \frac{1}{40 \, \text{M} [(5-1)-0]} = 6.25 \, \text{K.s.}$$

# As VDS decreases, RDS decreases and MOSFET conductance increases => for higher conductivity, less VDS is used.

>> NMOS is used as a pull-down circuit.

ex 17.2 VDD=10V, RL=1Ksz, Ko=2mA/V2, VT=1

Draw VTC.

VDD=

\* Partial differential of an NMOS ID expression

ex 17.4 for a lincon mode

$$I_D(lin) = K \left[ (VGS - VT) VDS - \frac{VDS^2}{2} \right]$$

$$dI_D(V_{GS}, V_{DS}) = \frac{dI_D}{dV_{GS}} dV_{GS} + \frac{dI_D}{dV_{DS}} dV_{DS} \rightarrow to know the slope$$

$$\frac{dID}{dV_{GS}} = KVDS$$

- \* high load resistance -> low current -> low power dissipation

- \* MOSFET cets have the lowest power dissipation amongst all digital circuits.

\* Static Power Dissipation (avg) [H,L].

$$P_{DD}(stat) = \frac{100 \mathcal{U} + 5 \mathcal{U}}{2} \times 5 = 262 \mathcal{M} \omega$$

- Cunnent at gate =0°

Sunnent con not

rustrict fan-out

- # fan-out is restricted

by propagation delay

which is determined by

CL

- During charging load (0/p D→H) (1/p H→D)

IL = ID = ICL = CL dVoit

- 2 During discharging of CL (ofp H-D) (ifp D-H)

Icl = CL d Vout = Il-ID

$I_L < I_D \Rightarrow I_{CL} \text{ is -ve } \Rightarrow I_{CL} = -C_L \frac{dV_{out}}{dt}$

Linear conducting pull - down

EX 17.6 Find maximum CL if ICRG = 50 JA, IDISC = -20 JA  $\Delta + = 1 \text{ Ms}$ ,  $V_{OL} = 0.5 \text{ V}$ ,  $V_{OH} = 5 \text{ V}$

#### SOLUTION :-

$$\int_{t_{1}}^{t_{2}} dt = \frac{C}{Ic} \int_{V_{1}}^{V_{2}} dV_{out} \rightarrow + \int_{t_{1}}^{t_{2}} = \frac{C}{Ic} V_{out} \int_{V_{1}}^{V_{2}} V_{1}$$

$$\Delta t = \frac{C}{Ic} \Delta Vout$$

$$\longrightarrow$$

CCRG = 50  $\%$   $\times \frac{1 \%}{(5-0.5)}$  = 11.1 pF

$$DCDISC = -20 \text{ M} \times 1 \text{ M} = 4.44 \text{ pF}$$

crow the choose

$$C = 11.1 pF$$

then  $\Delta + = \frac{11.1 \times 10^{-12}}{50 \times 10^{-6}} \times 4.5 = 10^{45}$

The choose

$$C = 11.1 \text{ pF then } \Delta t = \frac{1.11 \times 10^{-h}}{-20 \times 10^{-6}} \times (-4.5) = 2.5 \text{ Us}$$

- ₹ If we choose C<sub>L</sub> = 4.44 pF then Δt at discharging will be I Us and at charging il will be even less.

- => CL = 4.44 pF is the max CL allowed

- obvious since discharge writer is less than the charge current

- => FAN-OUT: is the max load capacitance that can be driven and mentain an acceptable switching time.

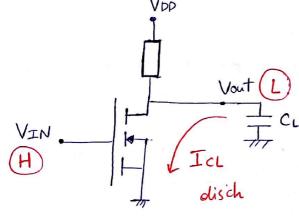

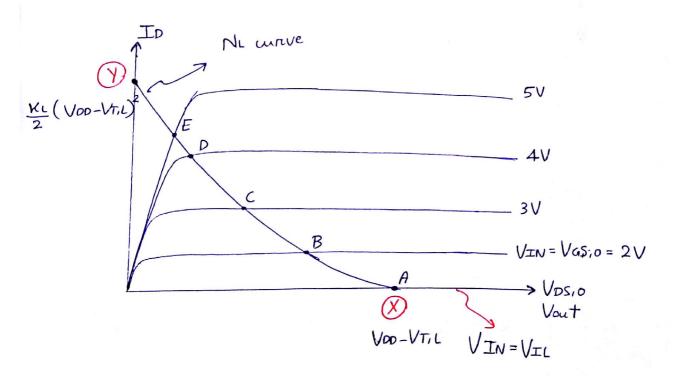

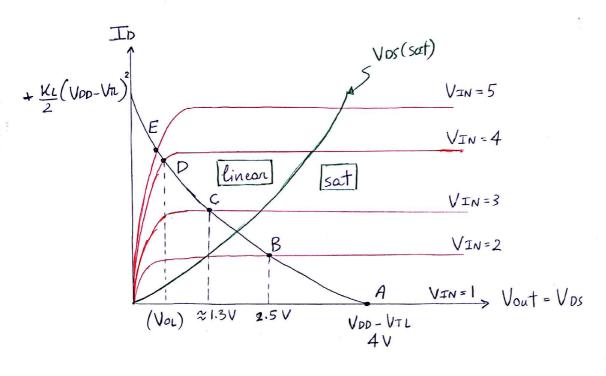

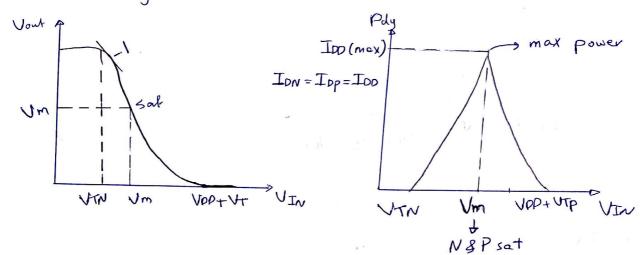

# CH. 19 Saturation Enhancement only loaded NMOS Inventer

\* NL operates in the saturation region, no metter in what mode No is operating

$$\frac{K_L}{2} \left( VGS_{,L} - V_{T,L} \right)^2 = 0 \longrightarrow VGS_{,L} = V_{T,L} = V_{DS_{,L}}$$

at VIN= VT,0

No turns to sat region and

2> at VIN > VT,0

No is sat and NL is sat

$$\frac{K_L}{2} \left( V_{GS,L} - V_{T,L} \right)^2 = \frac{K_0}{2} \left( V_{GS,0} - V_{T,0} \right)^2$$

VGS, O = VIN

بعد التعويض

VGS, L = VDS, L = VDD - Vout

In the previous equation k

$$\frac{\mathcal{K}_L}{2} \left( V_{PP} - V_{OUT} - V_{T,L} \right)^2 = \frac{\mathcal{K}_0}{2} \left( V_{IN} - V_{T,0} \right)^2$$

SOLVE FOR Vout

$$Vout = -\sqrt{\frac{K_0}{K_L}} V_{TN} + V_{TI0} \sqrt{\frac{K_0}{K_L}} + V_{DD} - V_{T,L}$$

during transformation from H to L

The larger Ko , the steeper the transition is.

when VIN = Vout = VM (No 8 Nc sat)

In one set VIN = Vout = VM and solve for VM

$$V_{M} = V_{DD} - V_{T,L} + V_{T,0} \sqrt{\frac{\kappa_{0}}{\kappa_{L}}}$$

$$1 + \sqrt{\frac{\kappa_{0}}{\kappa_{L}}}$$

$$\Rightarrow \frac{dV_{\text{Out}}}{dV_{\text{IN}}} = \left(\frac{dI_{\text{D,O}}}{dV_{\text{IN}}}\right) \left(\frac{dI_{\text{D,L}}}{dV_{\text{Out}}} - \frac{dI_{\text{D,O}}}{dV_{\text{Out}}}\right) = -1$$

Substitute for the partial derevatives and solve for Vont

From quadratic equations, find another relation between Vout & VIN and with eq. (4) solve for Vout & VIH

$$VIH = VT_{10} + \frac{2(VDD - VT_{1}L)}{\sqrt{\frac{3K_0}{K_L}} + 1}$$

Use eq. 4 to find Vout at VIH

Then

$$Vol = \frac{KL(Vob - VT,L)^2}{2 KL(Vob - VT,L) + 2 Ko(Vob - VT,L - VT,0)}$$

$$\pm D, L(sat) = \frac{KL}{2} (Vas, L - VT, L)^2$$

$$O = \frac{K_L}{2} \left( Vas, L - VT, L \right)^2$$

$$I_{DD}(oL) = I_{D,L}(sat) = I_{D,o}(lin)$$

$$= K_o \left[ \left( V_{GS,o} - V_{T,o} \right) V_{DS,o} - \frac{V_{DS,o}^2}{3} \right]$$

$$\Rightarrow \frac{\text{PDD}_{1}\text{stat}}{2} = \frac{\text{Idp}(OH) + \text{Idp}(OL)}{2} \text{VDD} = \frac{\text{Idp}(OL)}{2} \text{VDD}$$

$$\frac{ex}{L}$$

19.1 find critical points  $V_{DD} = 10V$ ,  $\left(\frac{\omega}{L}\right)_0 = \frac{10Jm}{5Jm}$

$$\left(\frac{\omega}{L}\right)_{L} = \frac{5V_{m}}{15V_{m}}$$

,  $K' = 20 VA/V^{2}$   $V_{T} = 1.2 V$  for No 8 NL

$$N_0 = \frac{10}{5} \times 20 \text{ MA/V}^2 = 40 \text{ MA/V}^2$$

$$\Rightarrow \frac{K_0}{K_1} = 6$$

$$K_L = \frac{5}{15} \times 20 \text{ J/A/V}^2 = 6.67 \text{ J/A/V}^2$$

from derived equations

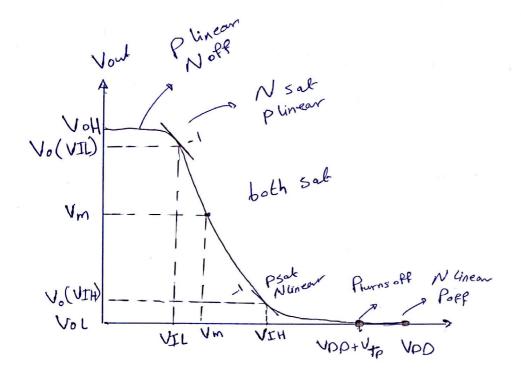

### CH. 23

$$N \rightarrow \text{off}$$

sat  $\lim_{n \to \infty} P \rightarrow \lim_{n \to \infty} s_n + \sup_{n \to \infty} s_n$

$$O = \mathsf{K}_{\mathsf{P}} \left[ \left( \mathsf{VsG}_{\mathsf{I}} \mathsf{P} + \mathsf{VTP} \right) \mathsf{VsD}_{\mathsf{I}} \mathsf{P} - \frac{\mathsf{VsD}_{\mathsf{I}} \mathsf{P}^{2}}{2} \right]$$

$$K \left[ \left( VGS, N - VTN \right) VDS, N - \frac{VDS, N}{2} \right] = 0$$

$$\frac{K_{P}}{2} \left[ V_{SG/P} + V_{T,P} \right]^{2} = \frac{K_{N}}{2} \left[ V_{GS,N} - V_{T,N} \right]^{2}$$

$$V_{DD} - V_{M}$$

$$\frac{KN}{2} \left[ V_{GS,N} - V_{T,N} \right]^2 = K_P \left[ \left( V_{SG,P} - V_{T,P} \right) V_{SD,P} - \frac{V_{SD,P}}{2} \right]^2$$

$$\frac{K_{N}}{2} \left[ V_{IN} - V_{T,N} \right]^{2} = K_{P} \left[ \left( V_{DD} - V_{IN} + V_{T,P} \right) \left( V_{DD} - V_{out} \right) - \left( \frac{V_{DD} - V_{out}}{2} \right) \right]$$

$$\frac{d I_{D,N}}{d V_{IN}} d V_{IN} = \frac{d I_{D,P}}{d V_{IN}} d V_{IN} + \frac{d I_{D,P}}{d V_{D,I}} d V_{OUT} \Rightarrow 0 = 2$$

$$\frac{dVout}{dVIN} = \frac{dID,N}{dVIN} = \frac{dID,P}{dVIN} = -1$$

$$\frac{dID,P}{dVout}$$

$$\frac{d I_{D,N}}{d V_{IN}} = \frac{d I_{D,P}}{d V_{IN}} = -\frac{d I_{D,P}}{d V_{Out}}$$

and Vout (VIL) is found from

$$ID,N(sat) = ID,p(lin)$$

$$\frac{\ln V}{2} \left( V_{IN} - V_{T,N} \right)^2 = \ln \left[ \left( V_{DD} - V_{IN} + V_{TP} \right) \left( V_{DD} - V_{OUT} \right) - \left( \frac{V_{DD} - V_{OUT}}{2} \right)^2 \right]$$

$$\frac{V_{IH} = V_{DD} + V_{T,P} + \frac{K_N}{K_P} (V_{T,N} + 2 V_{out})}{1 + \frac{K_N}{K_P}}$$

$$580 \left(\frac{w}{L}\right)_{N} = 230 \left(\frac{w}{L}\right)_{P}$$

$$= 7 \left(\frac{W}{L}\right)_{p} = 2.5 \left(\frac{W}{L}\right)_{N}$$

\* Static power dissipation = 0

design CMOS for symmetry (and check).

$$VDD = 5$$

,  $KN = 40MD$ ,  $VDD = 5$ ,  $KN = 40MD$ ,  $VDD = 5$ ,  $KN = 40MD$ ,  $VDD = 5$ ,

$$k_p = k_p' \left(\frac{w}{L}\right)_p = 16M \frac{10}{2} = \frac{80 MA}{V^2}$$

$$V_{m} = \frac{\sqrt{000}}{2} = 2.5$$

$V_{m} = \frac{5 + (-1) + 1\sqrt{\frac{80}{80}}}{1 + \sqrt{\frac{80}{80}}}$

$= 2.5 \text{ V}$

$$80 \left[ (VGS + VTN) VDS - \frac{5 - (V_{IL} + 2.5)^{2}}{2} \right]$$

$$= \frac{30M}{2} \left[ V_{IL} - I \right]^2$$

Fan out depends on load capacitance allowed, and still has an acceptable propagation delay.

- => tpHL: propagation delay when output "H -> L" input "L -> H"

- \* difference between input rising to 50% of max and output

- dropping to 50% of max.

DEPLH: time diffirence between input dropping to 50% and output Nison

Pull down Nison

- diz tpHL = [ 2 VTN + I (VOD-VTN) (n((1.5 VOD-NTN))] CL

- chi tplH = [ -2 UTP + 1 (1.5 VOD+ 2VTP)] CL OP [ kn(VDD+ VTP) 2 + kp (VDD+ VTP) (0.5 VDD )] CL

find CL from both equations and choose smaller one. Pison total capacitance of all loads.

FAN-OUT for symmetry

Capacitance Por single load.

CIN = ( W/ LN + Wp Lp') (0x.

6PHL

driver and load one identical.

CL = F CIN -O

Fanout

Por symm. (W)p = 2.5 (W)N

Por simplicity let Lp=LN.

CIN = (WN LN + Z.5 WN LN) COX

= 3.5 WN LN COX

KN = Kp

tw = MN Gx (W) N -- 2

$$= \frac{CL}{kN} = \frac{3.5 LN}{MN}$$

$$= \frac{Mn}{3.5 LN^2} \left( \frac{CL}{kN} \right)^{\frac{1}{2}} equation$$

### DIGITAL ELECTRONICS

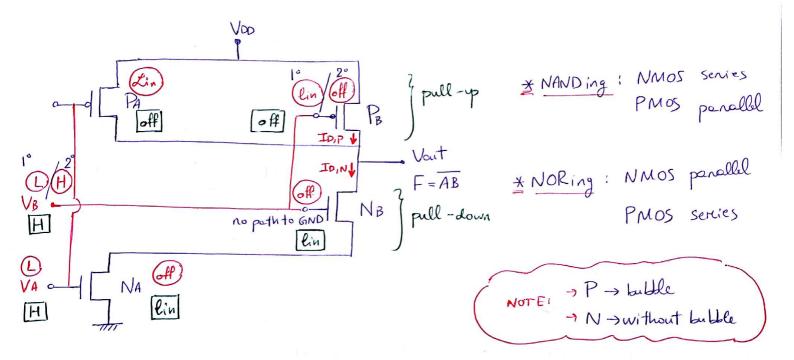

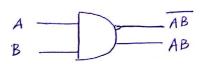

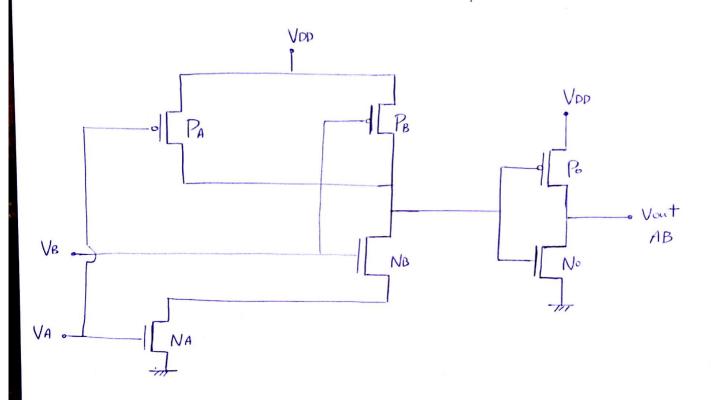

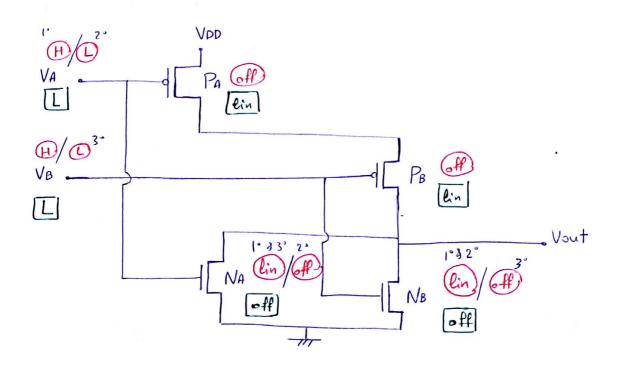

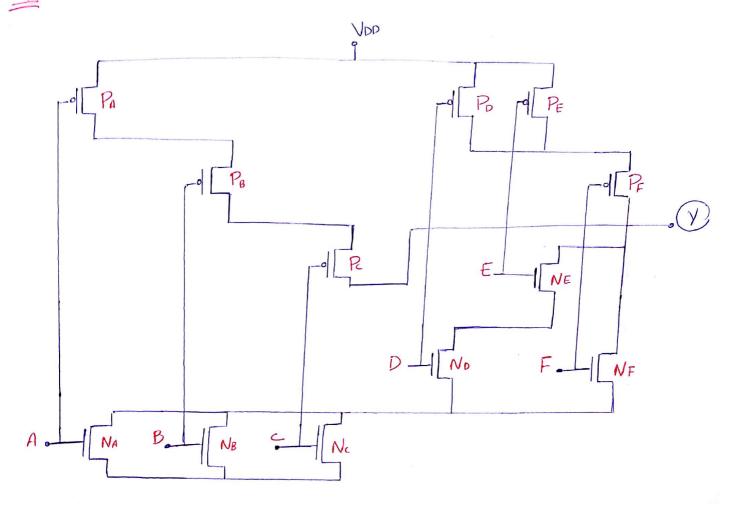

CH.24 CMOS Logic Gates

\* NAND CMOS Gote

- \* Output high state Amy on both inputs low

- O Both inputs low NAINB off PAIPB lin.

② Any input low: VA → L, VB → H

NA off, NB off (no path to ground)

PB off, PA lin ⇒ IDPA(lin)=0 ⇒ VSDA=0 ⇒ Vout = VOH = VOD

3 Any input low: VA -> H, VB -> L

4 All inputs high

#### AND / NAND

| 1    | 1 |          | 1       |

|------|---|----------|---------|

| A    | В | Vo, NAND | VO, AND |

| L    | L | Н        | L       |

| ا ال | Н | Н        | L       |

| Н    | L | Н        | L       |

| ↓ H  | Н | L        | Н       |

## > For summary

- O Single input WP = 2.5 WN LN

- 2 2 inputs NAND gate 2 WP = 2.5 WN LN

- 3 i inputs NAND gate i WP = 2.5 WN LN

### \* AND CMOS Gote

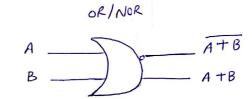

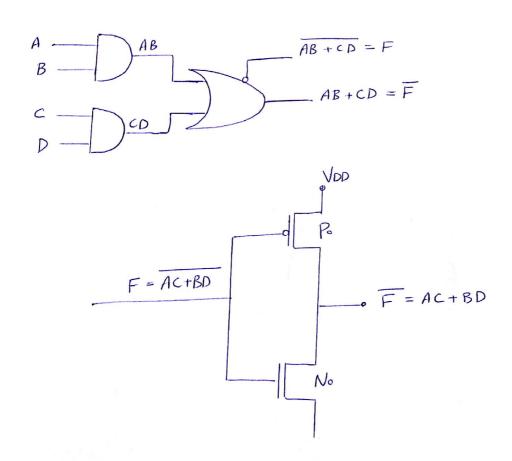

### \* NOR CMOS Gate

\* VOL

All or inputs high

1° → All high Ps off, Ns lin

2° → VA law , VB high

Rest one off

3°→ VA high, VB low

Rest are off

\* VOH

All inputs low

Ns off, Ps lin

VSD = O

Vout = VOH = VDD

| A | В  | Vo, Nor | Vo, or |

|---|----|---------|--------|

| L | L, | Н       | L      |

| L | Н  | L       | Н      |

| Н | L  | Ĺ       | Н      |

| Н | Н  | L,      | Н      |

### 2) For summary

- \* 2-inputs NOR Gate UP = 5 WN Lp

- \* i-inputs NOR Grate UP = 12.5 WN LN

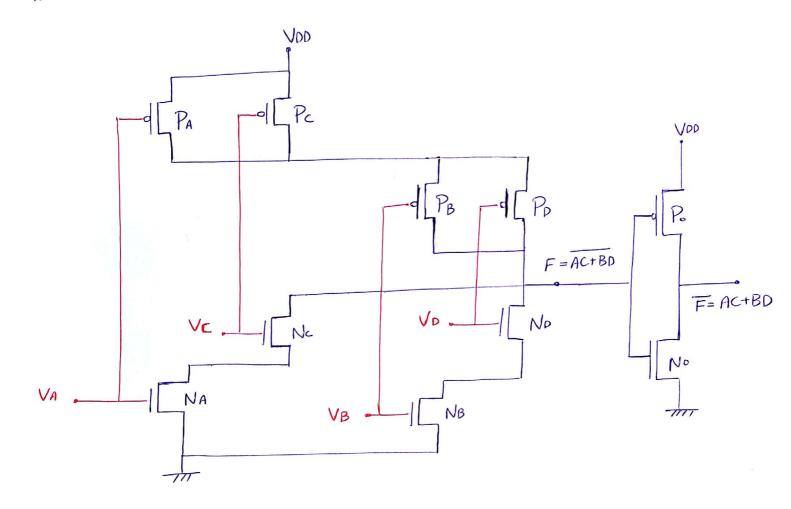

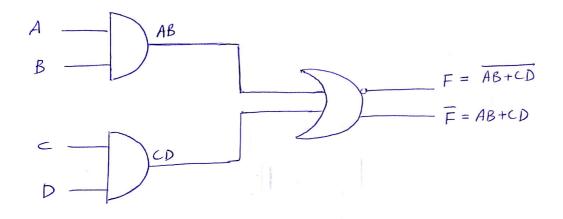

# # AND-OR Inventer Logic Function AOI

\* Keep inversion until the end

\* Enough to look at NMOS OR PMOS for NMOS: in services AC BD

in parallel AC + BD

for PMOS: in parallel AC BD

in services AC+BD

Ex Draw the function Y = (A+B+C)(DE+F) usig CMOS

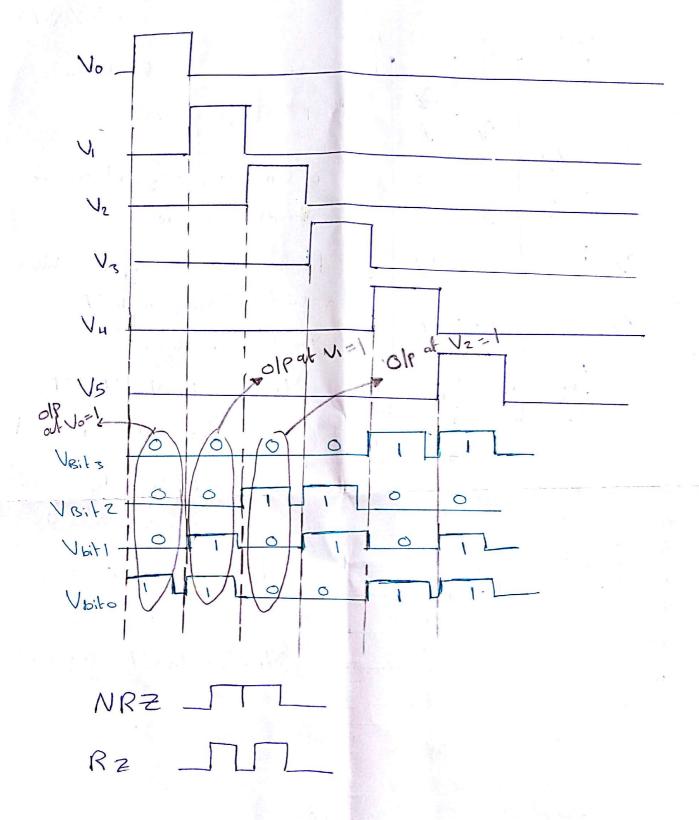

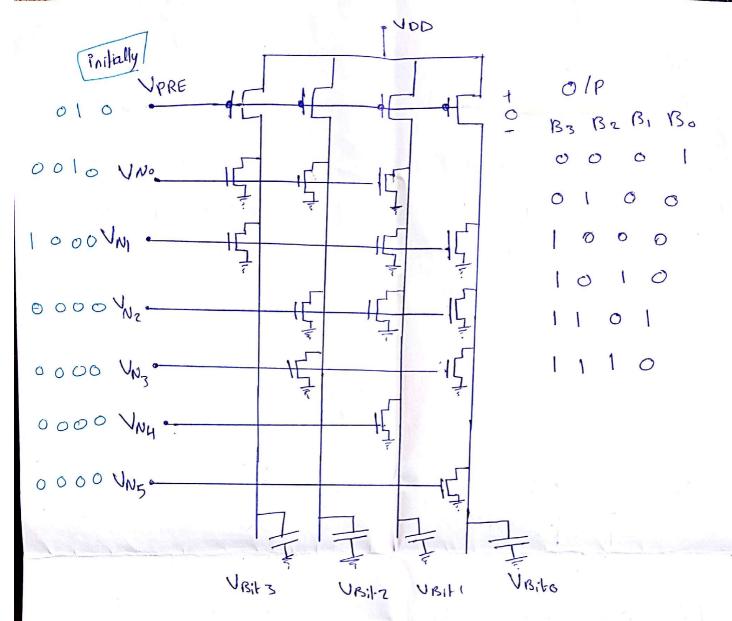

next , set Vi=1 and restistagic Zero and OIP.

Initially, VPRE is set at low, and all VN's one low, PMOS one linear and Voulput is high

=> Capacitaince will change to Upp. Next Uno is set at logic 1 and rest are 0. NMOS with input 1 is linear and Upsiv=6

Capacitors will discharge and olp is logic Zero,

NMOS with logic Zero will be off.

\* When all inputs at one gate one zero all NMOS will be off and Voul = VoH = VOD, logic (1)

\* Before setting  $VN_1 = 1$ , transistions need to be rest with all inputs (including VPRE) are set to zero, so that capacitous can change to VDD.

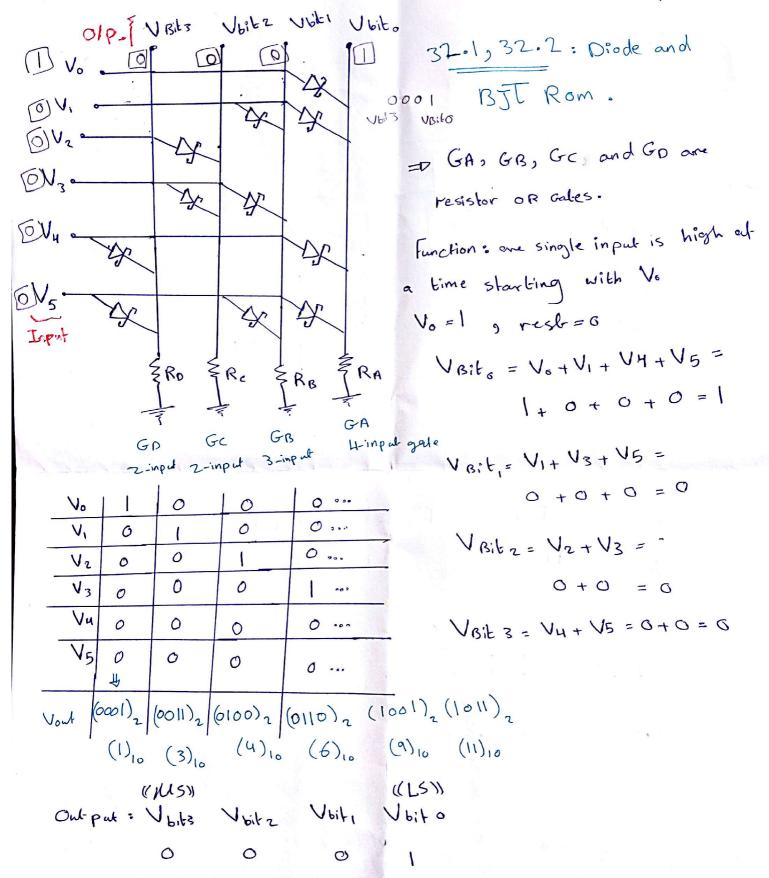

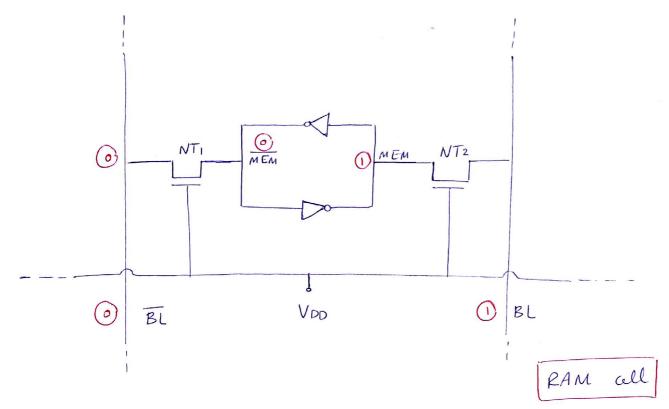

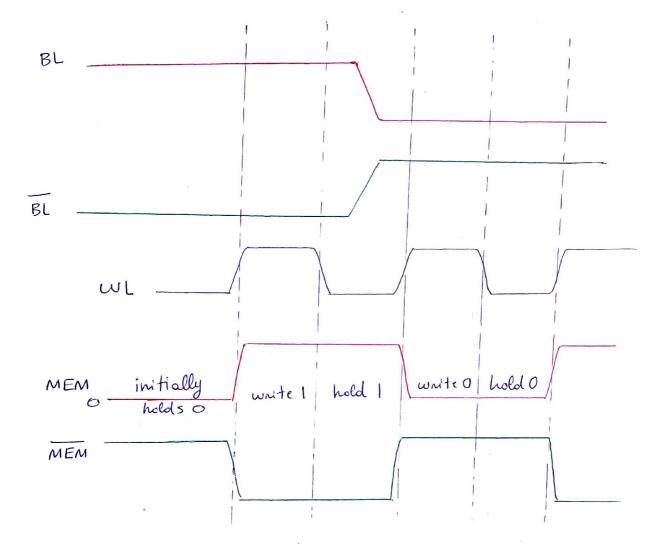

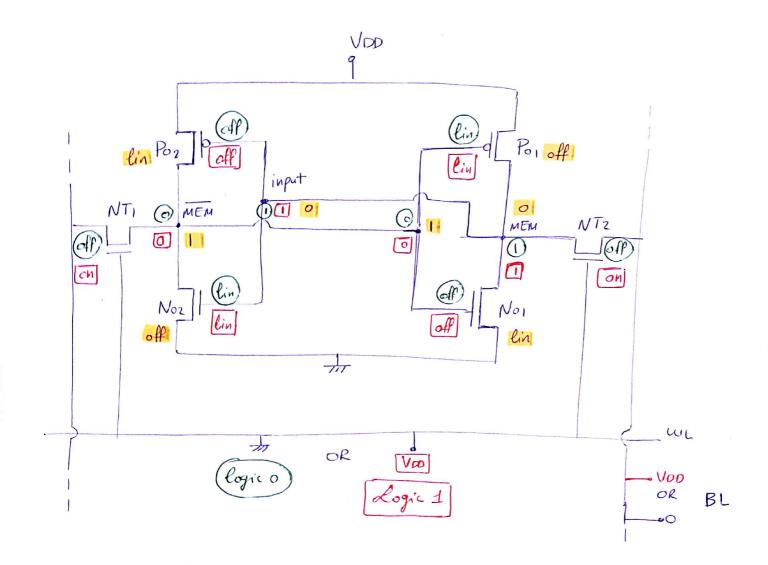

Chapter 33: Random Access memory

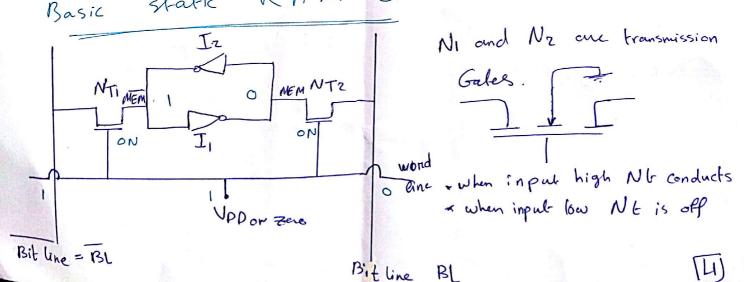

33.1, 33.2: Static RAM Cell with transmission gate.

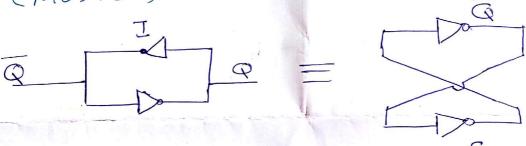

(MOSFET) Gross Coupled Inventer Latch.

RAM: Data can be read in a sequence independent of the order it was originally written.

SRAM: Maintains storage of Data as long as power applied to the semiconductor cet employing it is un-interupted.

Basic static RAM Cell

### DIGITAL ELECTRONICS

\* Writing data into cell

To write data, WL = 1

NT, & NT2 are on

MEM = 1 , MEM = 0

MEM = 0 , MEM = 1

Eleading data from all

WL = 1, BL & BL are allowed

to read data from all

## DIGITAL ELECTRONICS

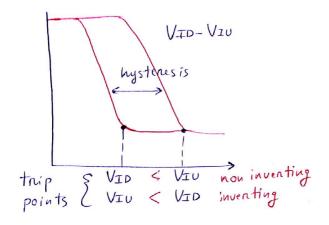

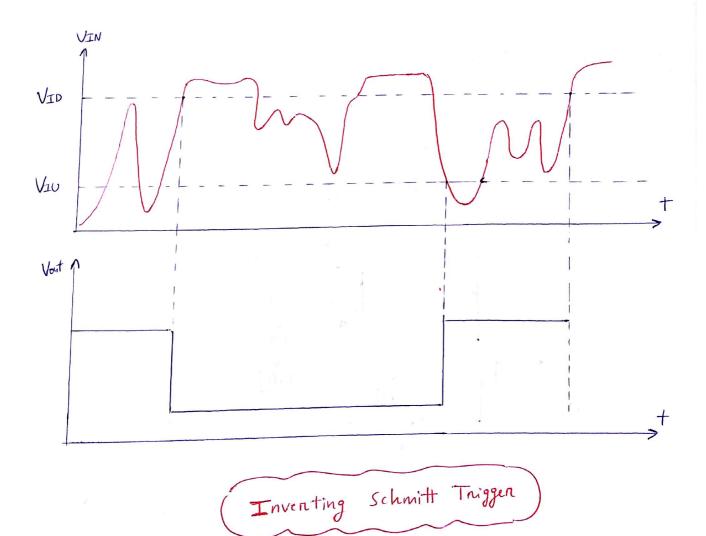

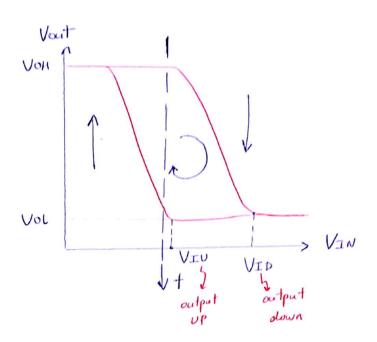

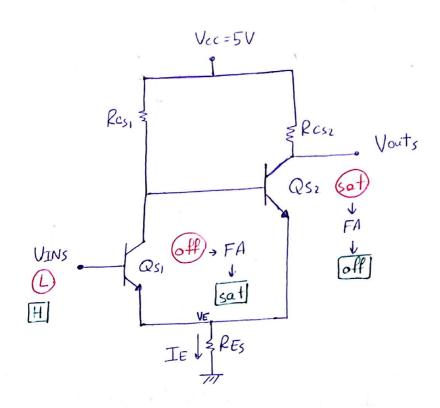

## 10.6 Shmitt Trigger

## \* Emitten Coupled Shmitt Triggen

$$VE = \frac{Vcc - V_{RE}(sat)}{Rcs_{1}} + \frac{Vcc - VcE(sat)}{Rcs_{2}}$$

$$\frac{1}{Rcs_{1}} + \frac{1}{Rcs_{2}} + \frac{1}{RE}$$

Initial VE from previous step

$$V_{IUS} = \frac{V(c - V_{BE_2}(s_{ot}))}{Rcs_1} + \frac{V(c - V_{CE_2}(s_{ot}))}{Rcs_2} + V_{BE_1}(FA)$$

$$\frac{1}{Rcs_1} + \frac{1}{Rcs_2} + \frac{1}{RE}$$

$$VID_{S} = Vcc + \left(\frac{R_{CSI}}{R_{E}} + 1\right)V_{BE,SI}(sat) - V_{BE,IS2}(FA)$$

$$\frac{R_{CSI}}{R_{E}} + 1$$

Q, sat

Q2 off

initially

Q2 -> set

just for shmitt

from TTL cct